计算机组成原理 第三章

第三章:存储系统

存储系统概述

存储器的存储结构

程序的局部性

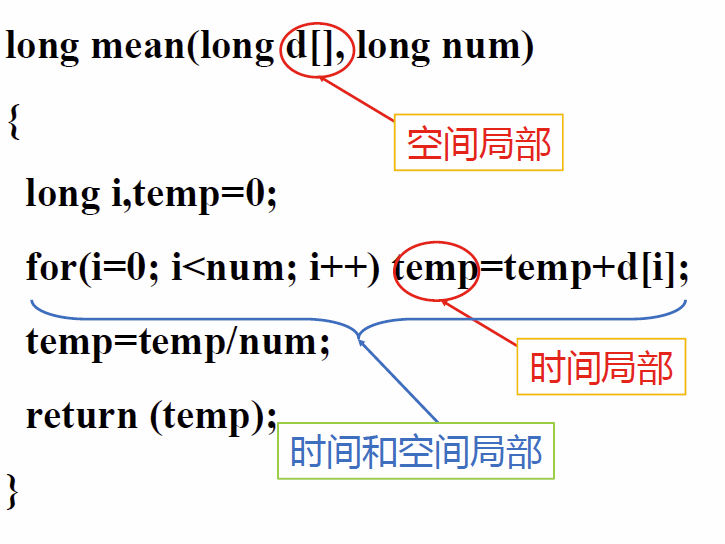

在某一段时间内,频繁访问某一局部的存储器地址空间,而对范围以外的地址空间很少访问

时间局部性:最近被访问的信息很可能还要被访问

空间局部性:最近被访问的临近地址的信息也可能被访问

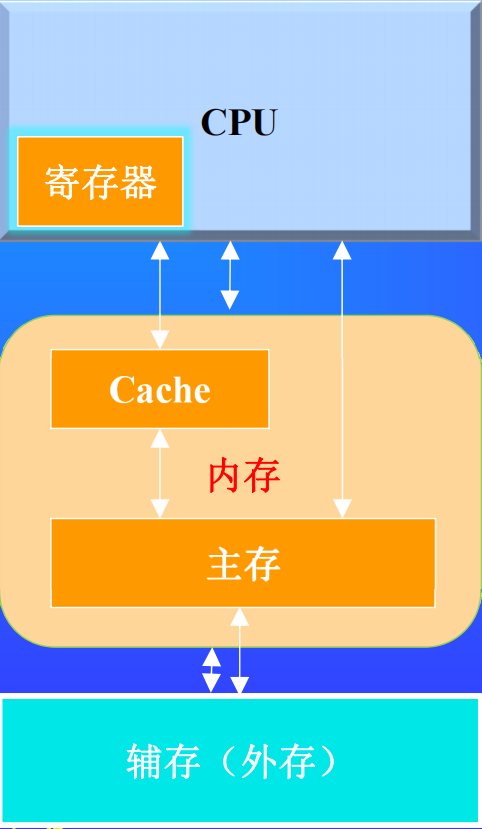

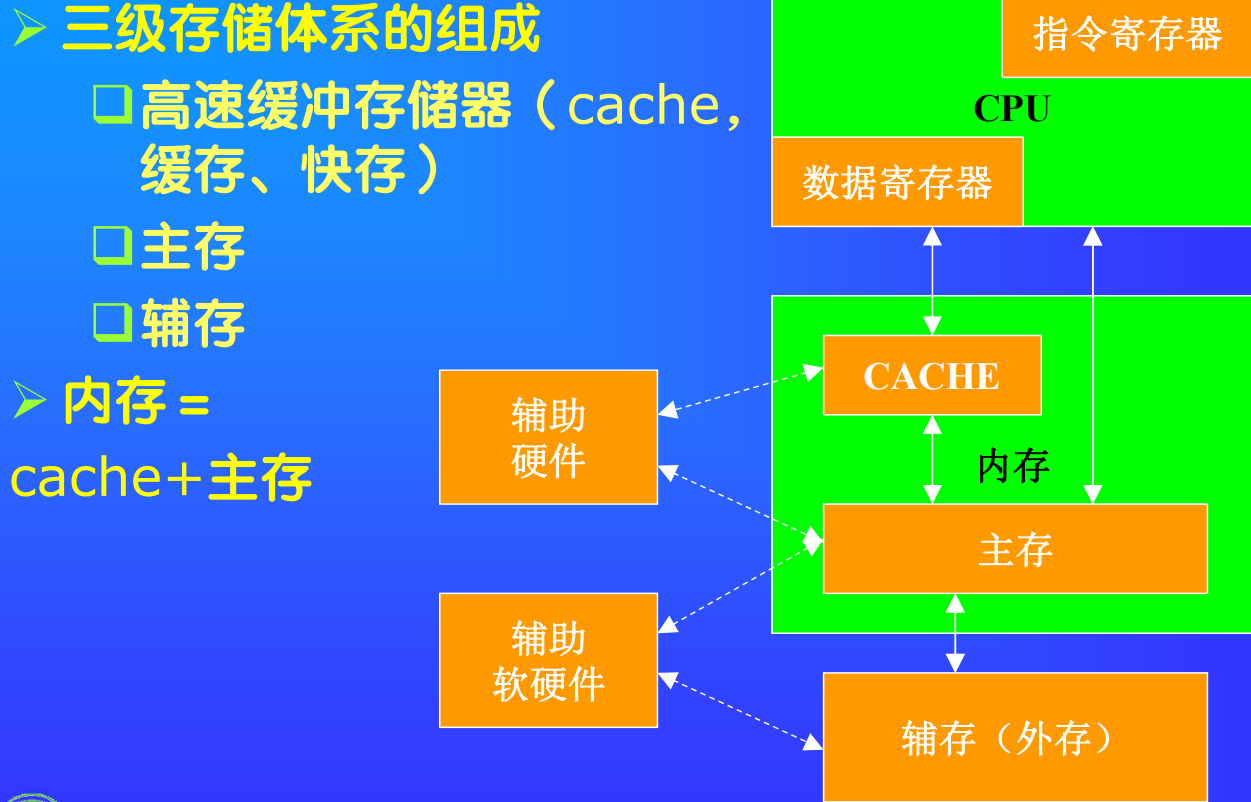

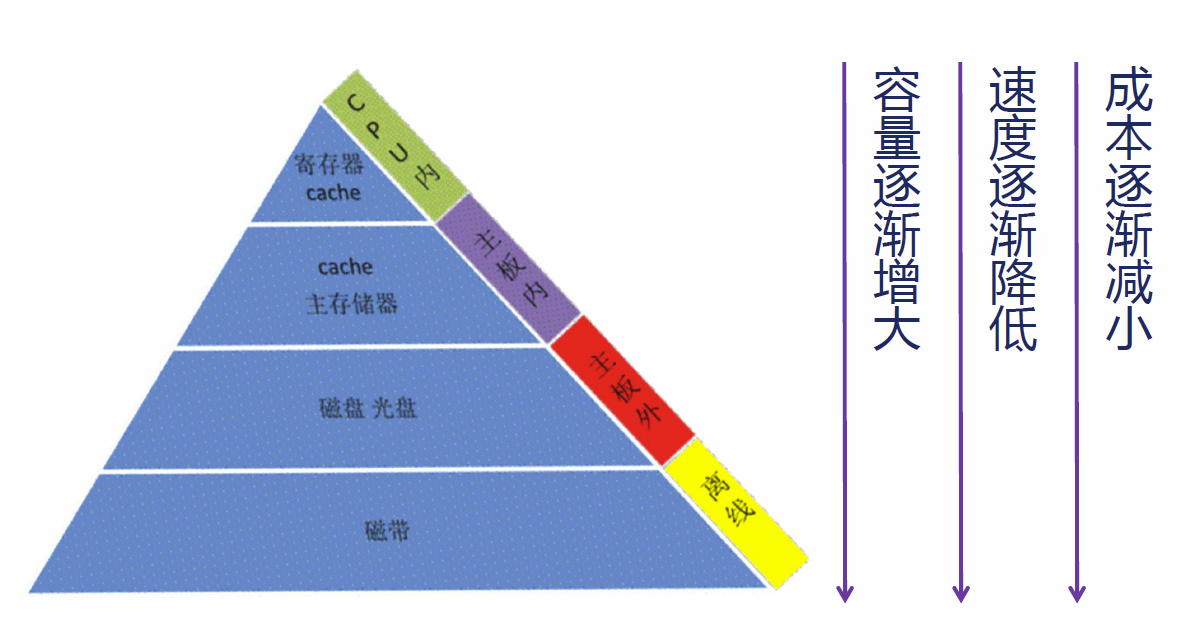

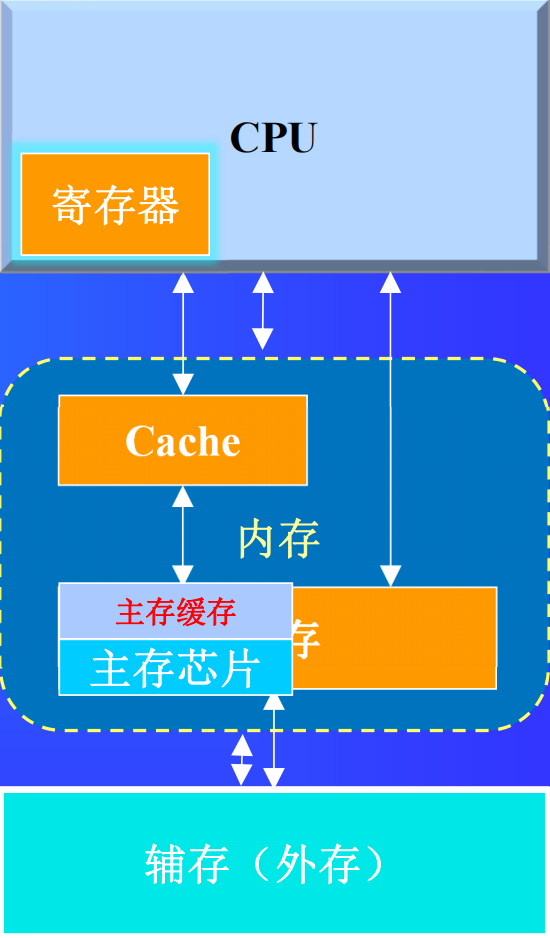

多级存储体系的组成

CPU内部寄存器:速度高、数量少

内存:速度高、容量小、价格高,由半导体器件构成,cache:更主要解决速度要求

外存:速度低、容量大、价格便宜,多由非半导体器件构成,主要为解决存储容量要求

出发点:提高存储系统的性能-价格比—— “多快好省”

整个存储系统在速度上接近cache,而在容量和价格上接近外存

两级存储体系的组成:内存、外存(辅存)

三级存储体系的组成:

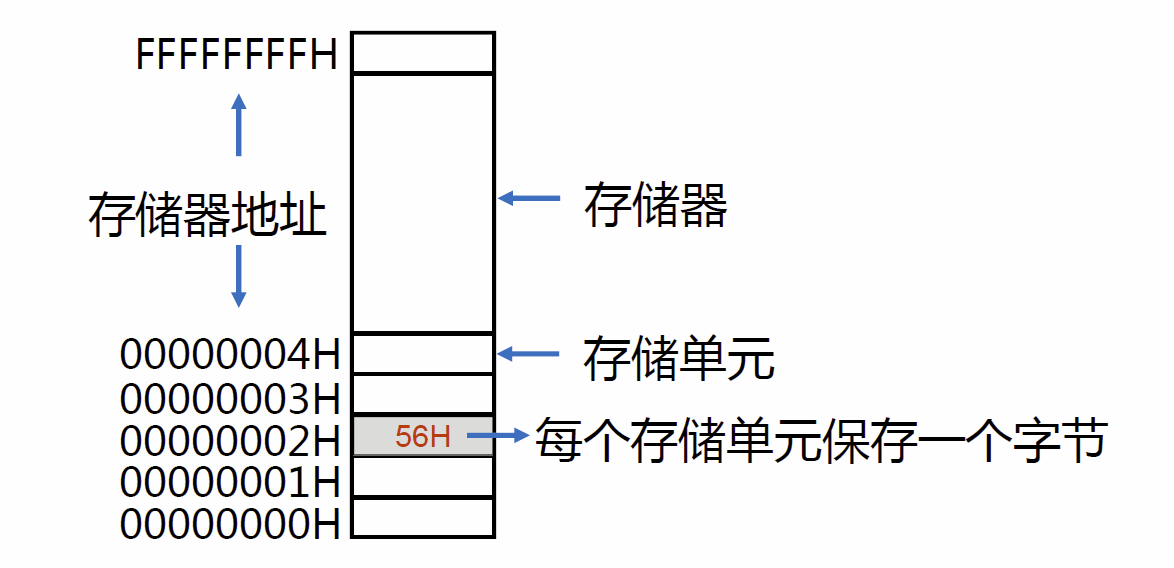

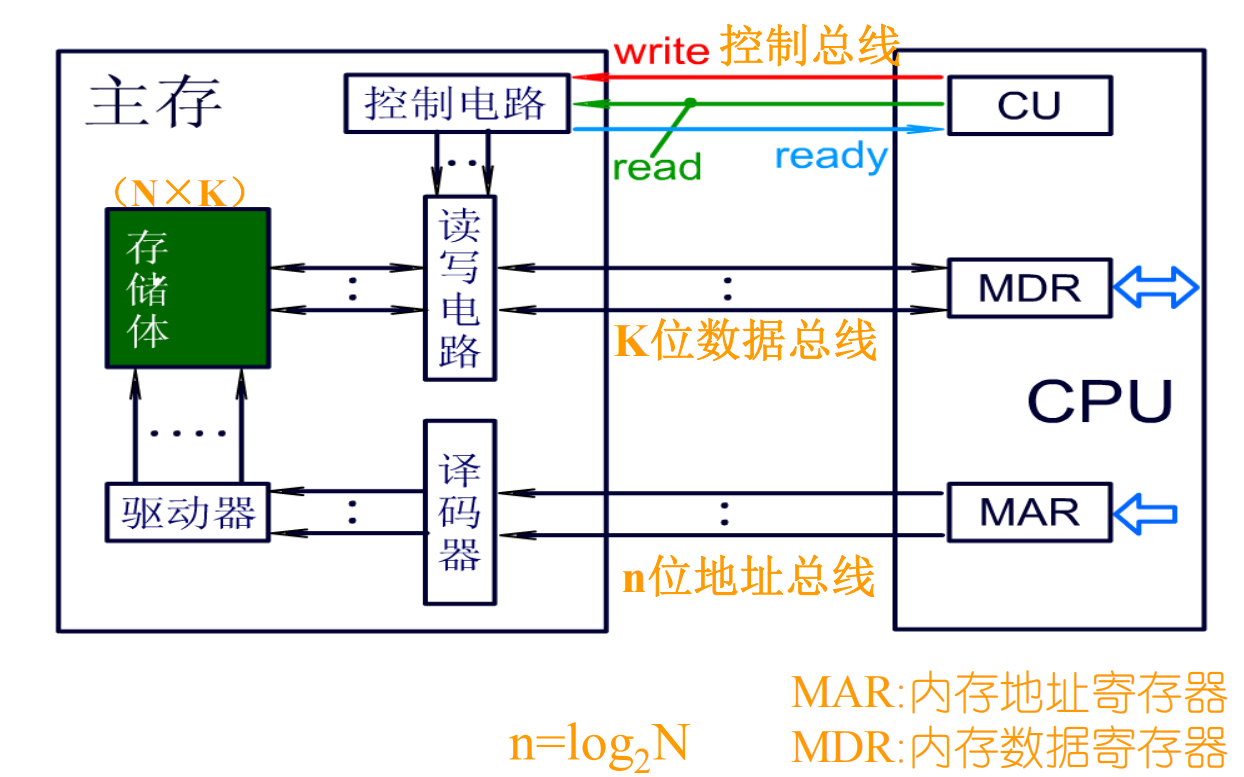

内存储器的编址方式

编址方式——存储系统中存储器地址的组织方式,编址方式在设计处理机时确定,每个存储单元有一个地址

按字节编址

按字编址

按半字编址

按1/4字编址

存储器访问

每次访问存储器读写的信息量:

字寻址:每次访存读写一个存储字

- 字:即CPU字长,等价于ALU一次能进行多少二进制位运算

半字寻址:每次访存读写半个存储字

字节寻址:每次访存读写一个字节

端模式

大端:高有效字节放在内存的低地址端,低有效字节放在内存的高地址端

小端:低有效字节放在内存的低地址端,高有效字节放在内存的高地址端

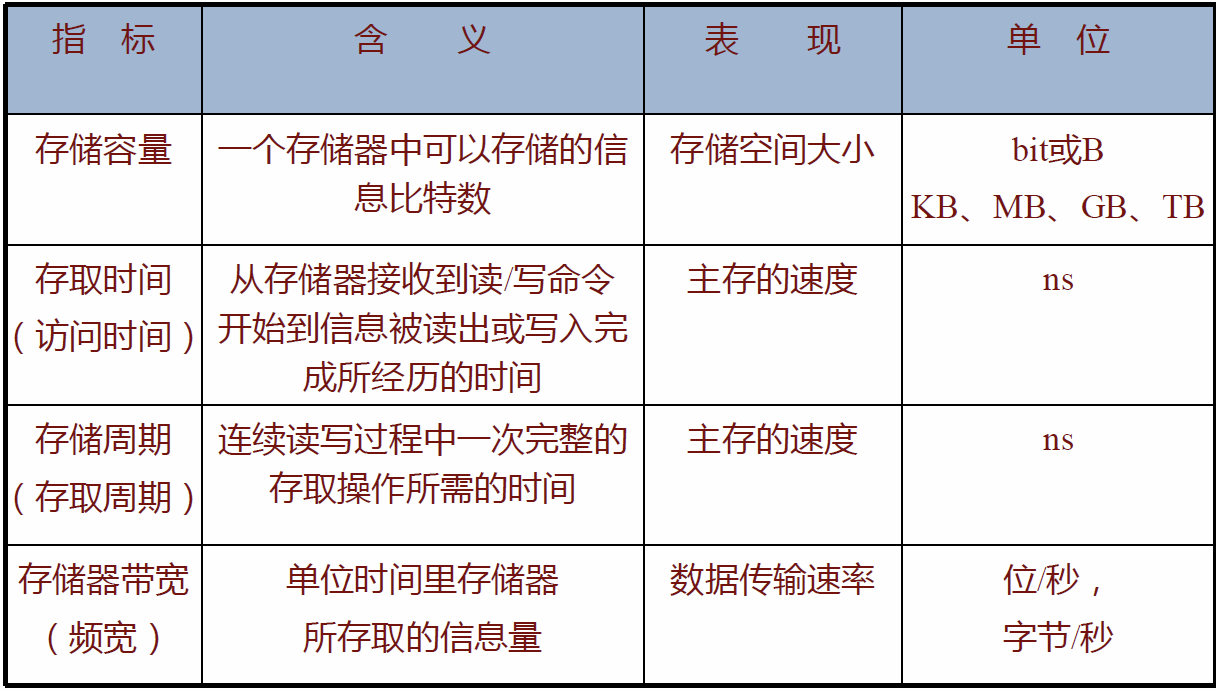

内存的主要技术指标

存储容量

通常表示为:存储字数(存储单元数) × 存储字长(每单元的比特数)

例:1M比特的存储器可以组织成

1M×1比特

128K×8比特

256K×4比特

存取速度

访问时间(存取时间)$T_A$:

决定于存储介质的物理特性和寻址部件的结构存取周期$T_M$:

CPU连续两次访问存储器的最小时间间隔数据传送速率(频宽)$B_M$:

若系统的总线宽度为 W bit,则 $B_M=W/T_M(b/s)$

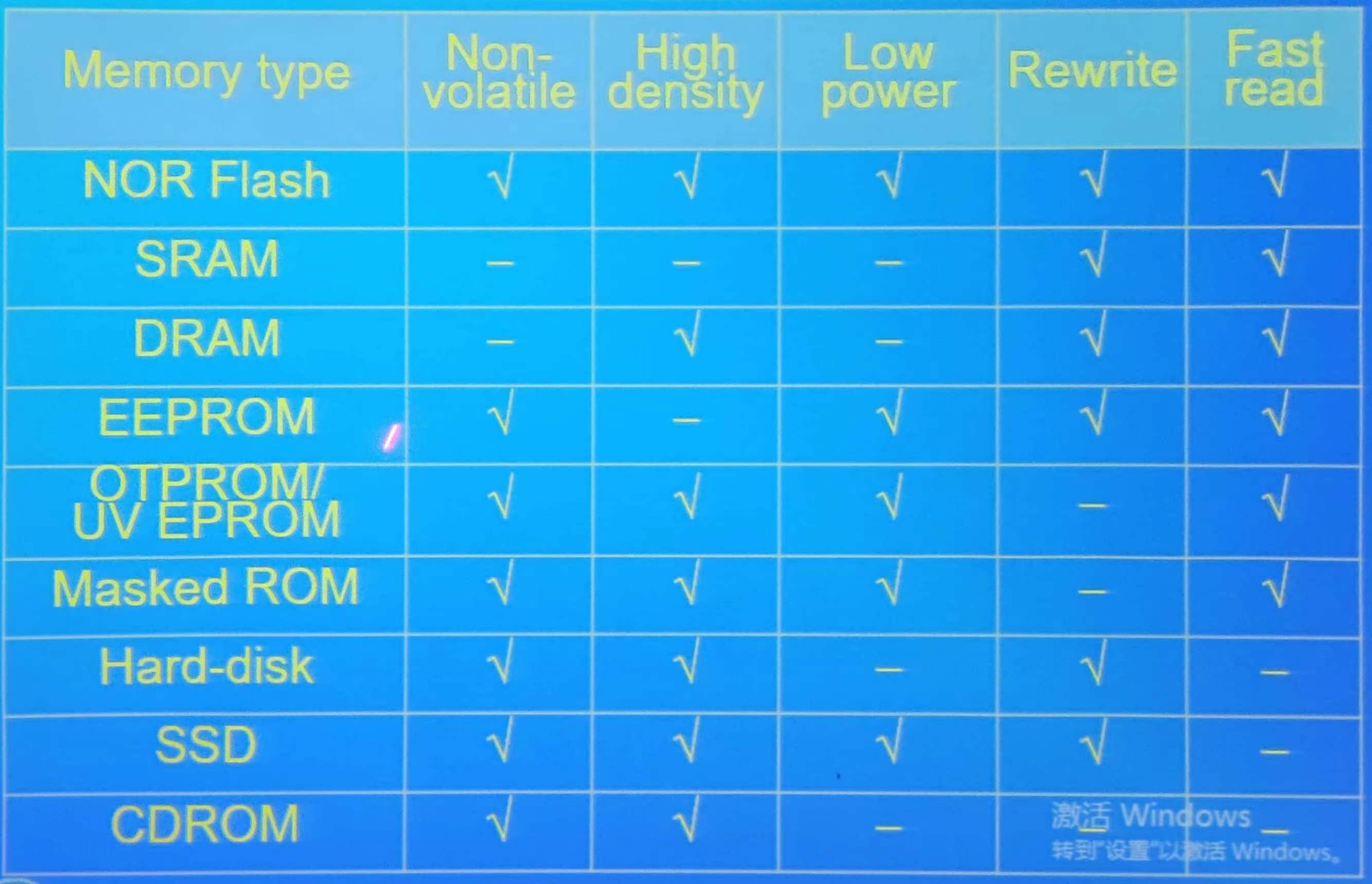

存储器的分类

存储介质:主要采用半导体器件和磁性材料

存储位元:存储一位二进制代码,是存储器中最小的存储单位

由若干个存储位元组成一个存储单元

由许多存储单元组成一个存储器

从存储介质上区分,可分为

半导体存储器、磁性材料存储器、光存储器。从存取方式 上区分,可分为

随机存取存储器、顺序存取存储器、半顺序(直接)存取存储器。从读写功能上区分,可分为

随机存取存储器(RAM)和只读存储器(ROM)从信息易失性上区分,可分为

易失性存储器、非易失性存储器。从与CPU的耦合程度上区分,可分为内部存储器和外部存储器,其中内部存储器又包括

主存,高速缓冲存储器。从掉电后存储的信息可否保持上区分,可分为

易失性(挥发性)存储器,非易失性(不挥发)存储器。从访问的串并行性上区分,可分为

并行存取存储器,串行存取存储器。从时钟特性上区分,可分为

同步存储器,异步存储器从存储器的访问方式上区分,可分为

按地址访问的存储器,按内容访问的存储器(CAM,相联存储器)从半导体存储器的信息储存方法上区分,可分为

静态(static)存储器,动态(dynamic)存储器从存储器的功能上区分,可分为

系统存储器,显示存储器,控制存储器……

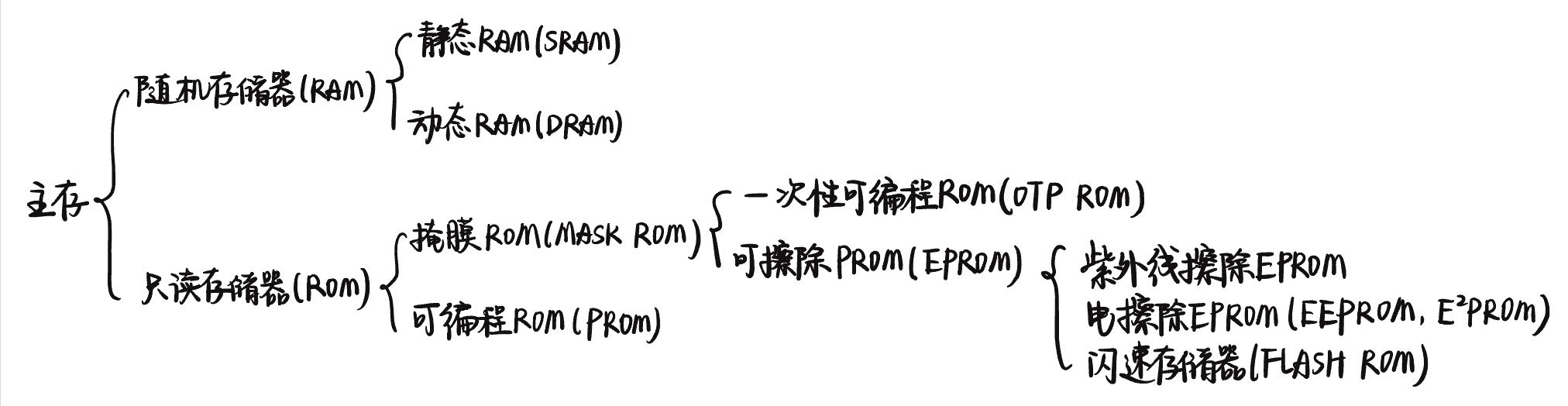

主存的分类:

随机读写存储器(RAM)

按介质分类:

- 双极性半导体存储器

- 金属氧化物半导体存储器

- SRAM

- DRAM

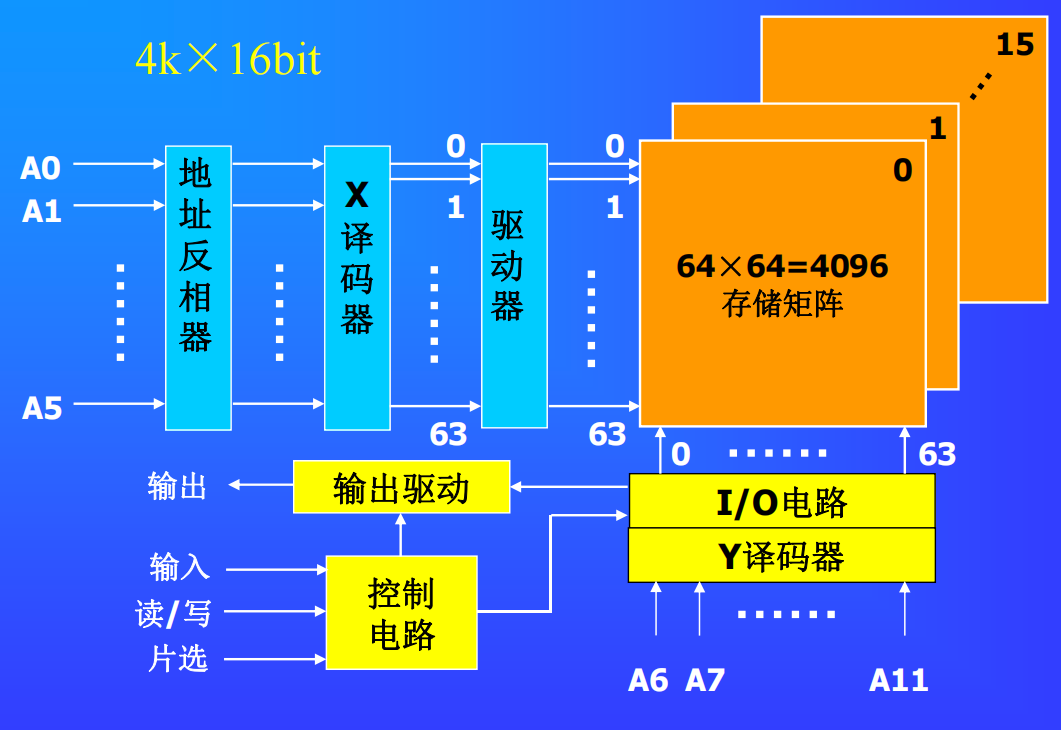

静态随机存取存储器(SRAM)

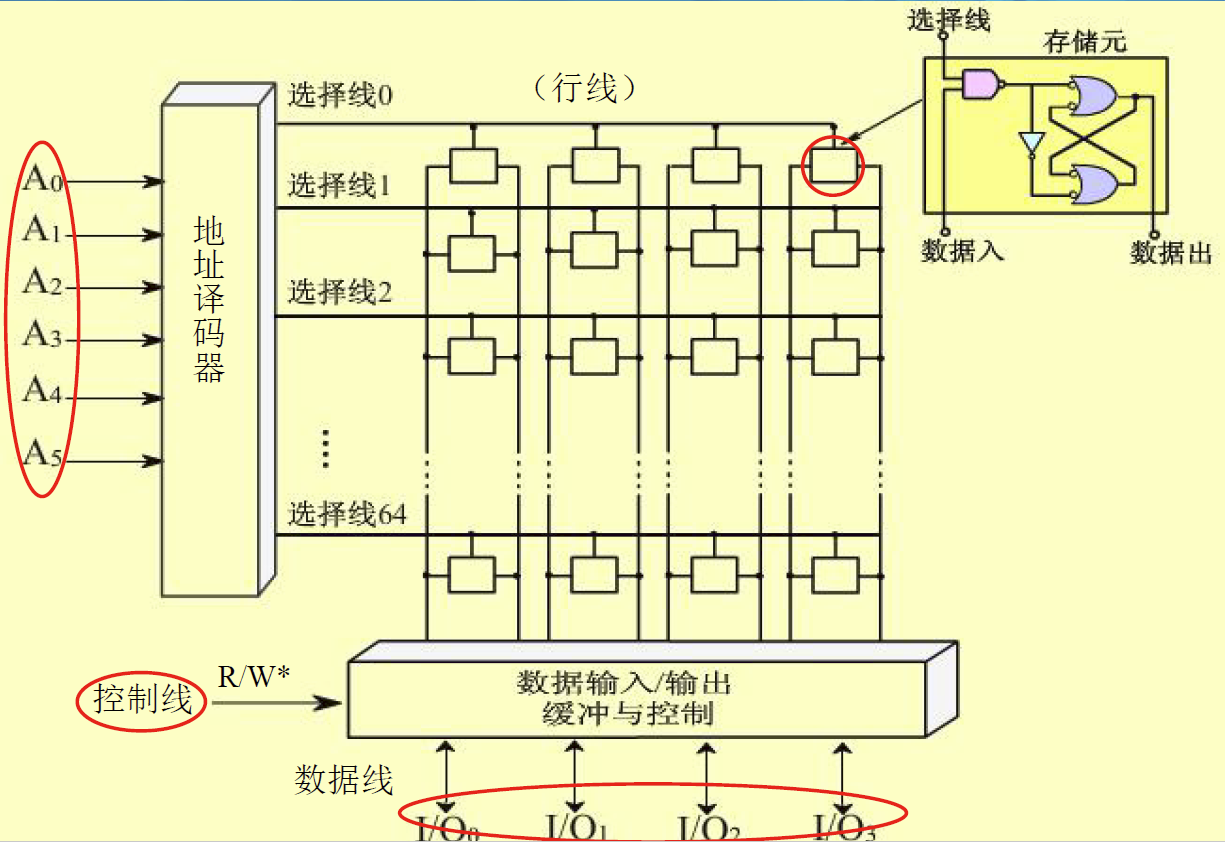

基本的静态存储元阵列

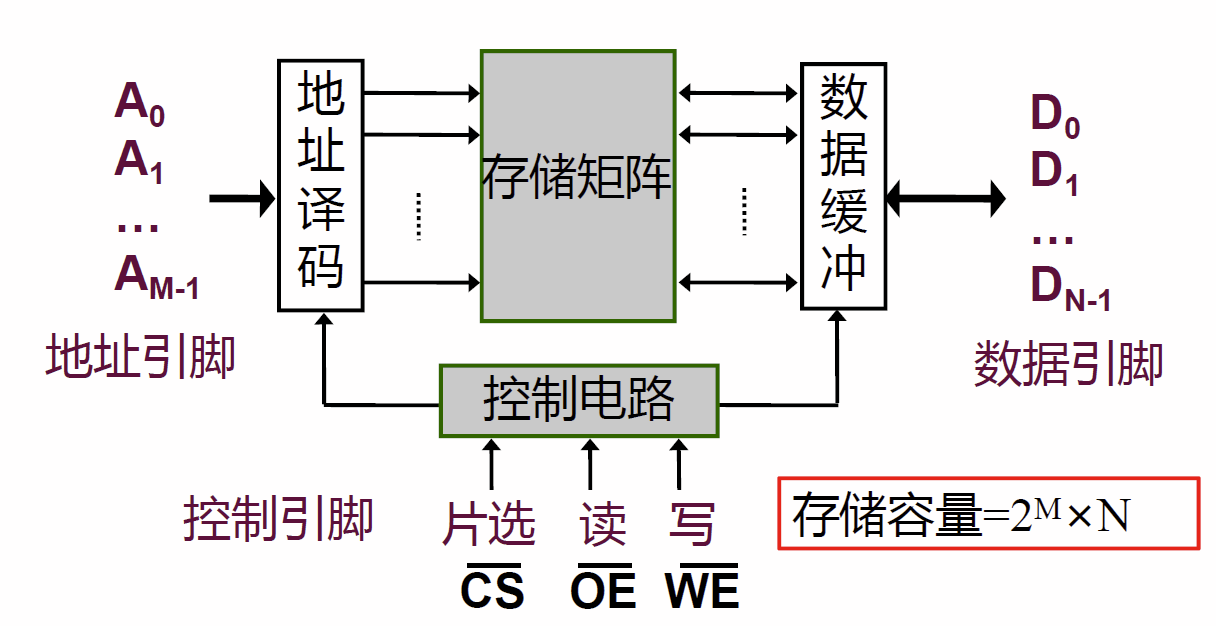

存储器芯片的基本结构

基本的静态存储元阵列

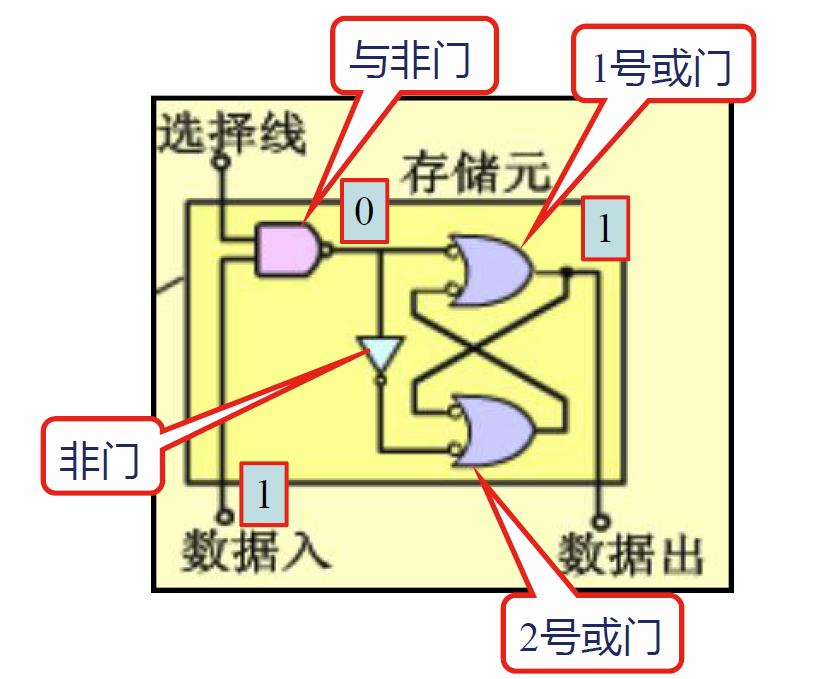

SRAM存储元电路

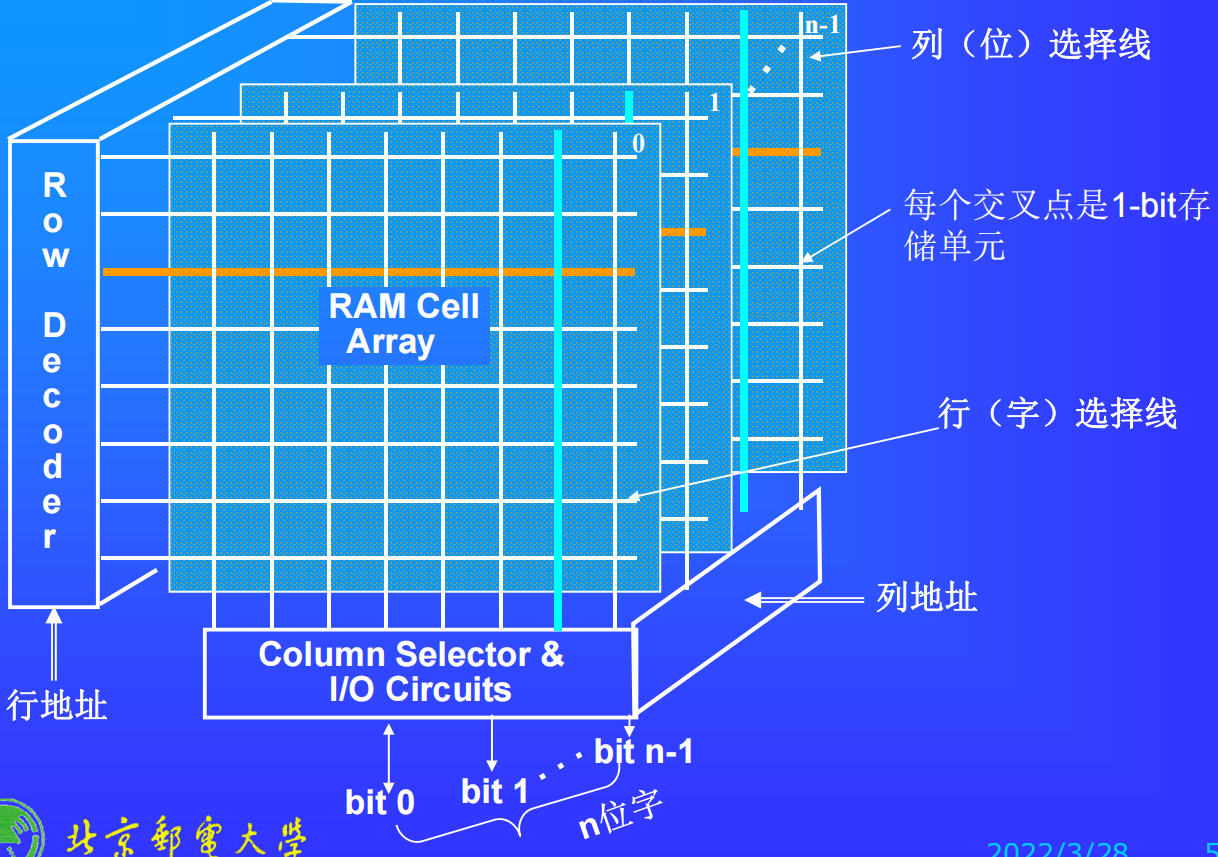

n位存储器芯片的结构

每条行选择线要控制n(一行n比特)×m(m个平面)个基本存储元

每条行选择线要控制n(一列n比特)×m(m个平面)个基本存储元

地址线与数据线

- 地址线的作用:地址线的作用就是决定了数据的存储单元的位置,也决定了你有多少个能够存放数据的存储单元个数,这点不懂没关系,后面会解释的。

- 数据线的作用:数据线的作用就是决定了二进制的数据。

- 举个例子:地址线就是你家的门牌号,数据线就是待在家里边的你。比如现在有人想要找你,就要通过门牌号来找到你,也就是通过地址线来找到数据线决定的数据。

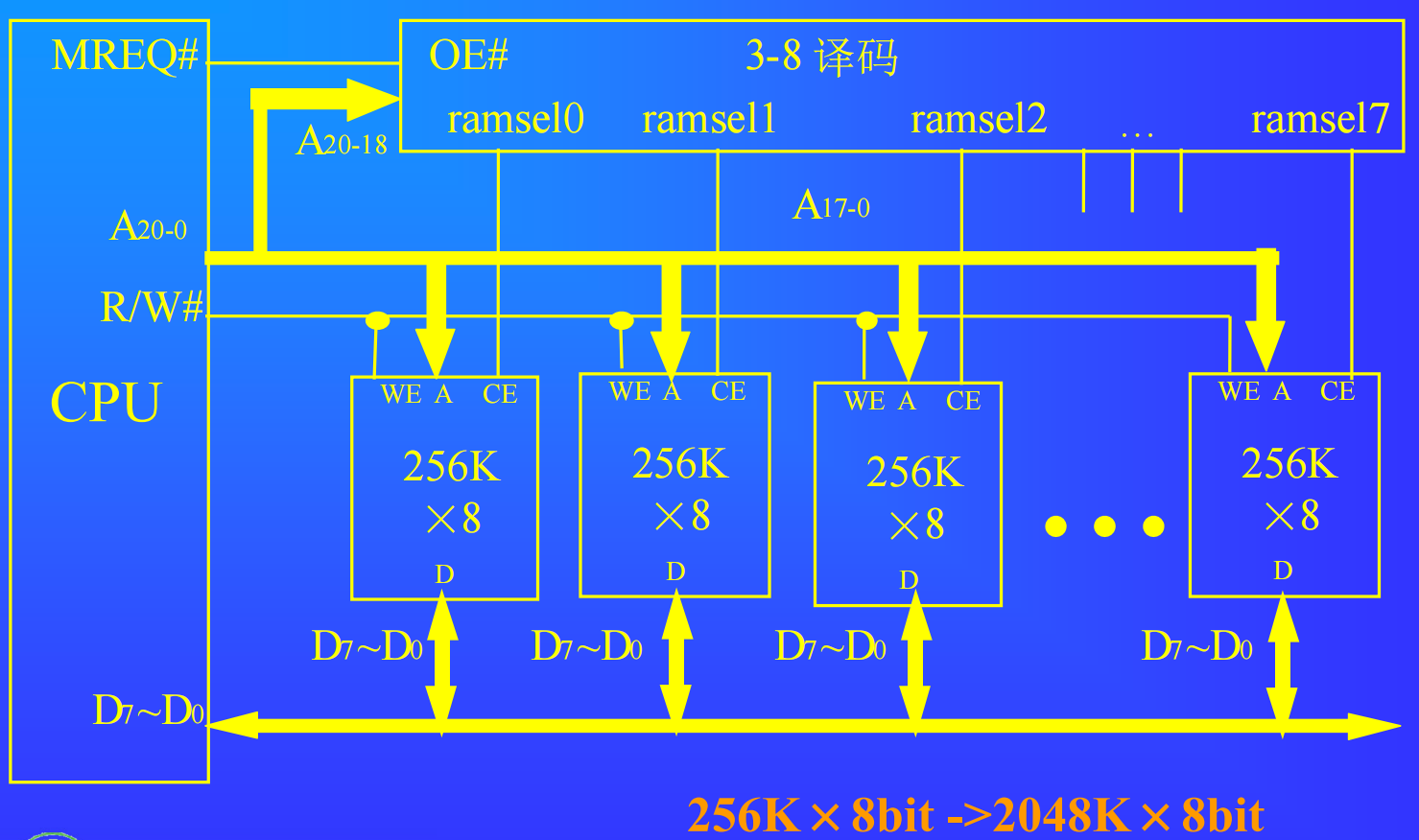

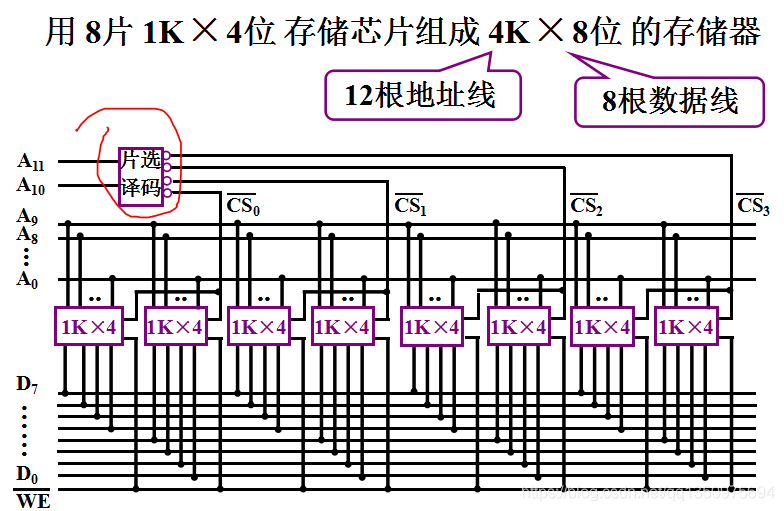

字扩展与位扩展

Xk × X位 其中Xk就是代表字扩展里的字,X位就是代表位扩展里边的位。

- 字扩展

字扩展就是要增加存储字的数量,也就是地址线的位数

举个栗子:现在我能搜索的门牌号范围只有一个村,现在我想能够搜索到一个镇的门牌号,怎么办?当然是要扩大能够搜索的范围呀,字扩展就是起到的这么一个作用。

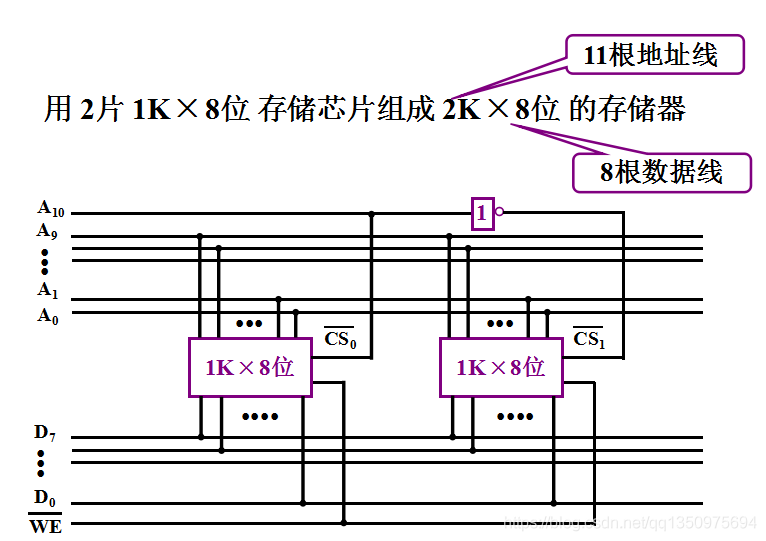

例如利用1K×8位的DRAM芯片,设计2K×8位的DRAM存储器(字扩展)

这里为什么要把A10设置成片选端呢?因为它们不能同时工作,每个芯片提供8位数据,在数据线上会造成混乱,A10做片选信号,控制选中哪个芯片。- A10等于0的时候范围是:A10A9A8A7A6A5A4A3A2A1A0\=00000000000-01111111111B\=0-1023

第一个芯片会工作,当A0到A9都为1时再增加A10就会变为1此时根据图可以看出CS0非\=1是高电平,A10在经过一个非门使CS1非接收到0,此时第二个芯片工作,从10000000000=1024开始。 - A10等于1的时候范围是:A10A9A8A7A6A5A4A3A2A1A0\=10000000000-11111111111B\=1024-2047

扩展之前是0-1023,扩展之后是从0-2047.

这样就形成了字扩展。对应了上边的地址线作用中的定义,这样就扩大了存储单元的个数。

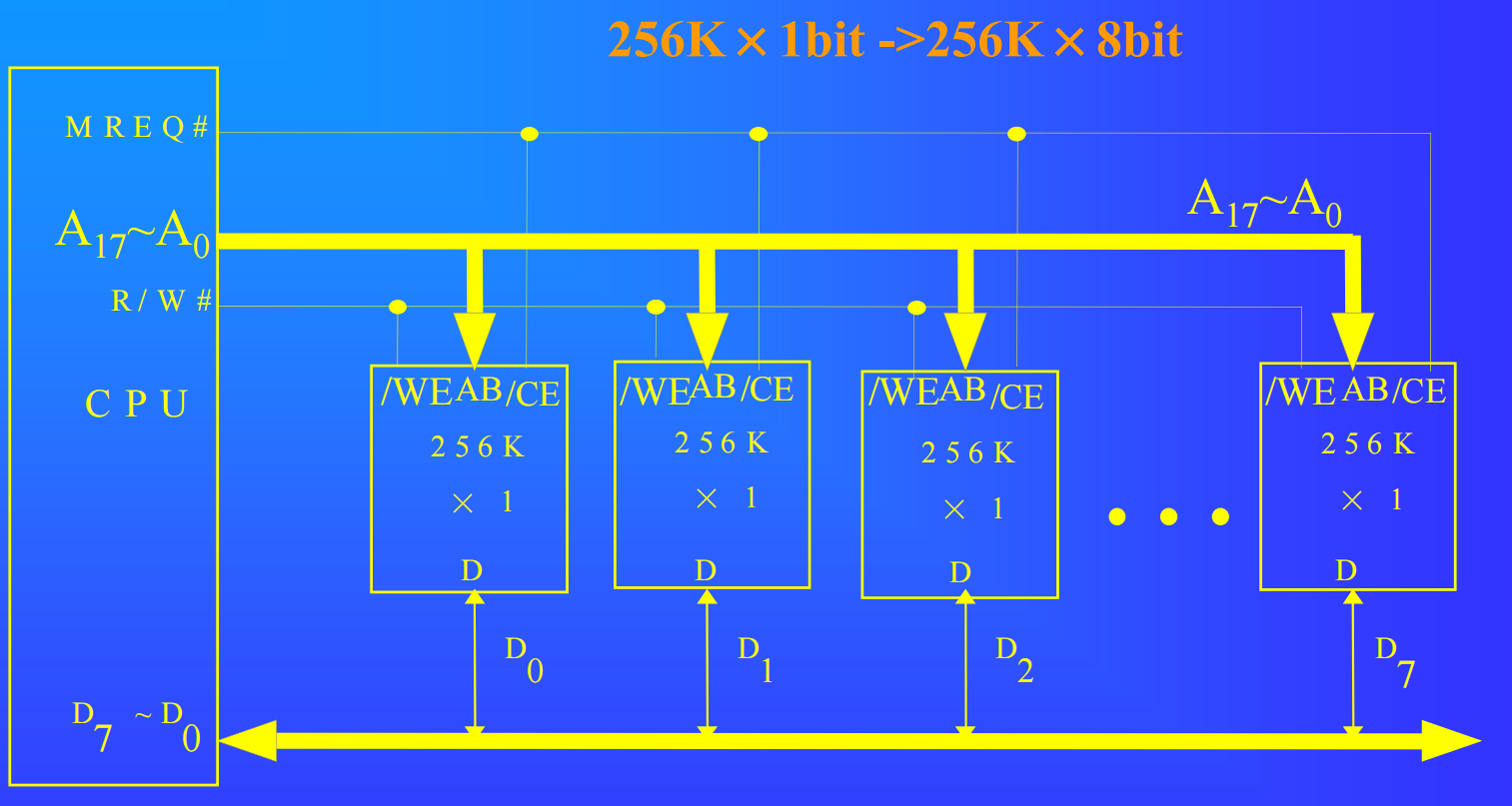

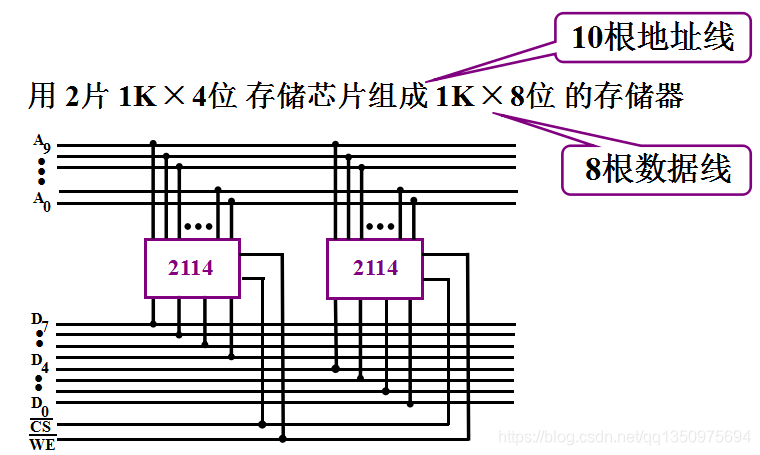

位扩展

位扩展就比较简单了,位扩展就是增大数据的范围,原本是四位D0到D3对应范围是0000-1111B\= 0 - 15;变为八位之后是D0到D7对应范围变成00000000 - 11111111B\=0 - 255;对应的图上的连线两个芯片八根数据线从D0到D7。一个芯片是数据的高四位,一个芯片是数据的低四位。

扩展之前是0-15,扩展之后0-255.

因为他们的地址线是连在一起的所以地址的范围两个芯片是一样的,对应的数据的地址也是一样的,取数据的时候根据地址取出第一个芯片的四位和第二个芯片的四位,最后形成八位的数据。

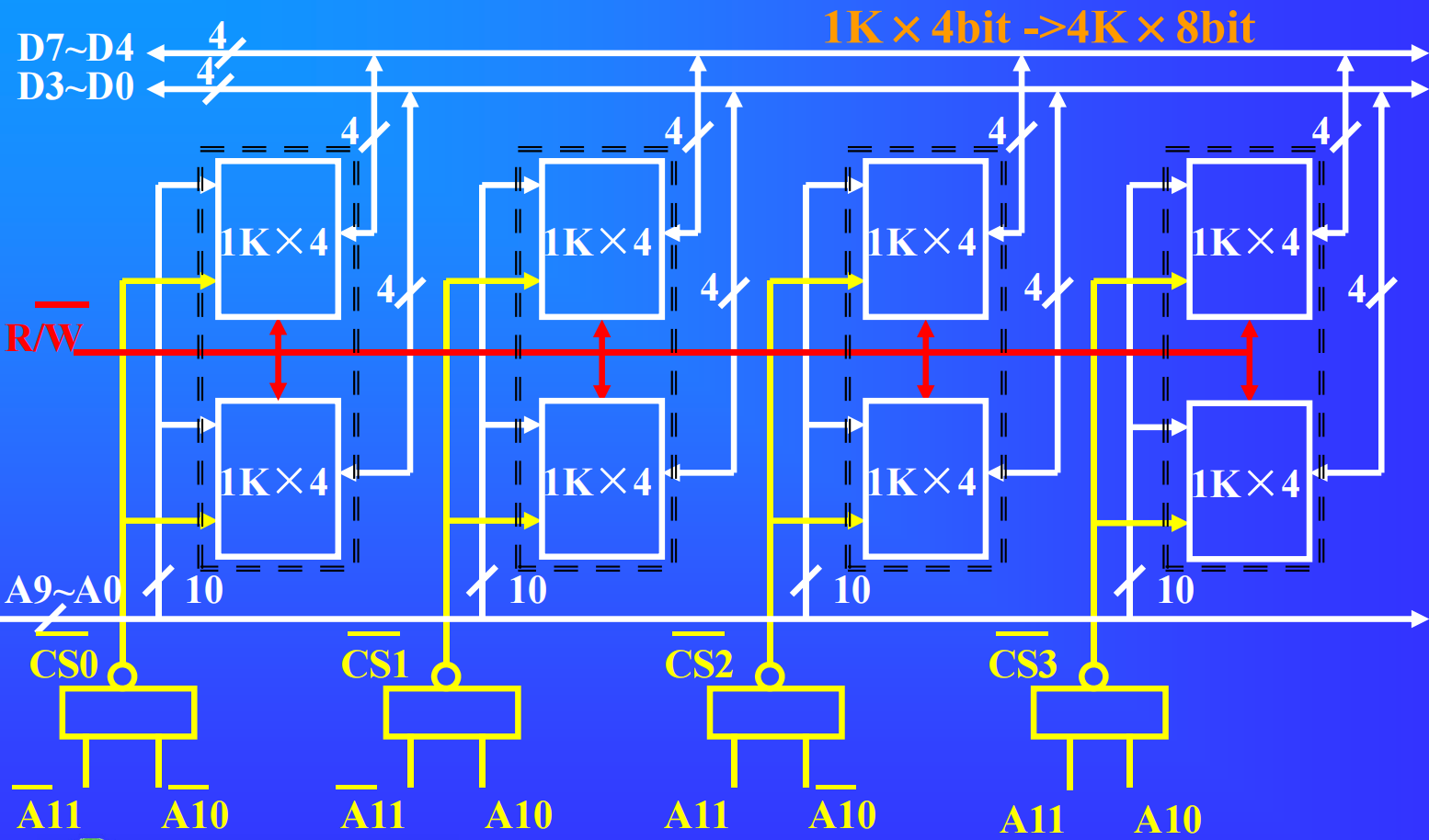

字位扩展

这里A11A10两个二进制数可以有00,01,10,11四种情况对应了四组二个芯片组成的八位存储器的选择。若有八个的话就要有A12A11A10三个二进制数000,001,010,011,100,101,110,111来代表八组二个芯片组成的八位存储器。

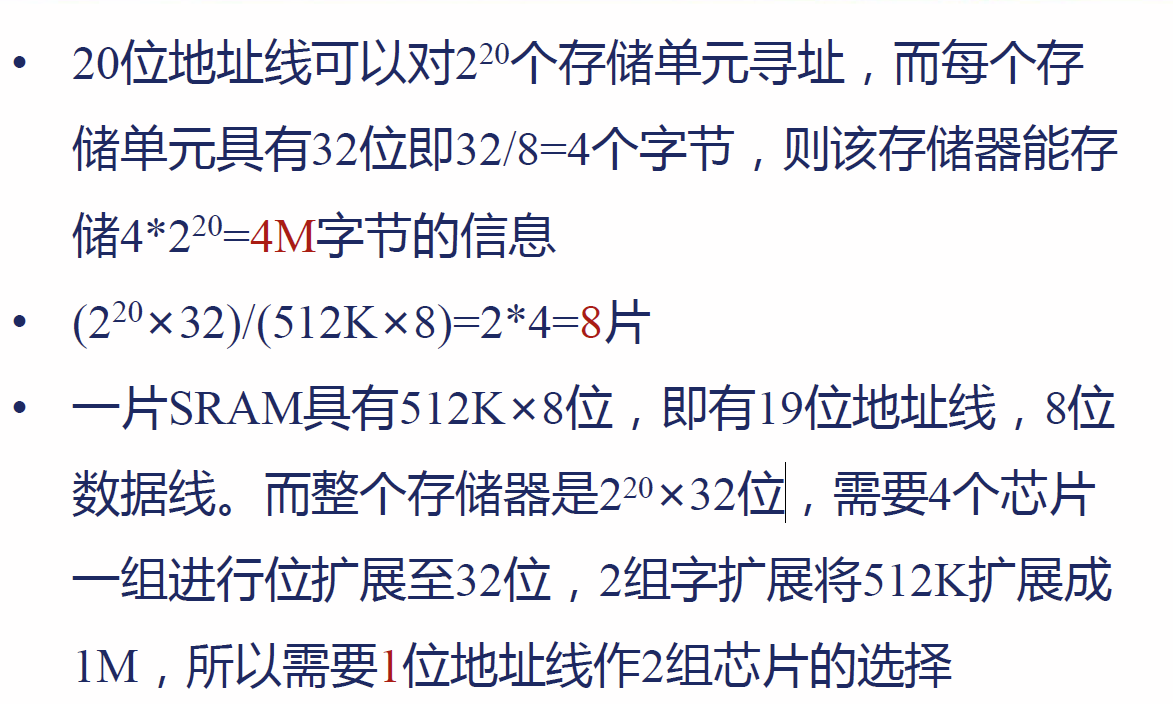

例题:

设有一个具有20位地址和32位字长的存储器,问:

- 该存储器能存储多少个字节的信息?

- 如果该存储器由512k*8位SRAM芯片组成,需要多少片?

- 需要多少位地址作芯片选择?

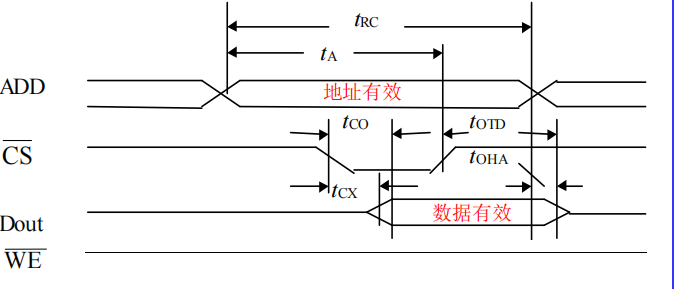

SRAM时序——读周期

$t_{RC}$:读周期,指对芯片连续两次读操作之间的最小间隔时间。

$t_{A}$:从给出有效地址后到数据在外部数据总线上稳定出现所需的时间。

$t_{CO}$:片选到数据输出延迟的时间。

$t_{CX}$:片选到数据输出有效的时间。

$t_{OTD}$:片选无效后数据还需在数据总线上保持的时间。

$t_{OHA}$:地址失效后,数据线上的有效数据维持时间,以保证所读数据可靠

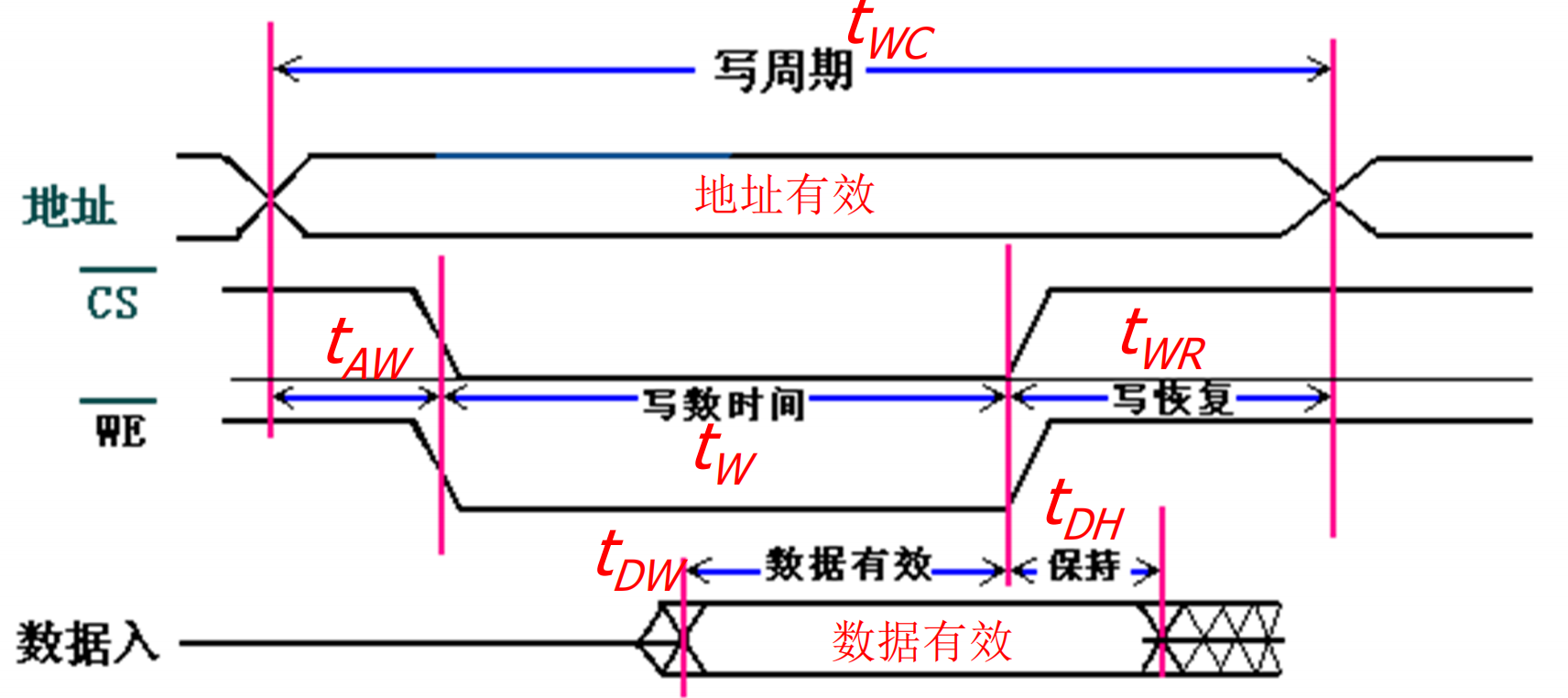

SRAM时序——写周期

$t_{WC}$:连续两次写操作之间的最小时间间隔。

$t_{AW}$:滞后时间,地址有效后,等待WE信号有效。

$t_W$:写数时间。

$t_{DW}$:写入数据必须在写无效之前tDW时间就送到数据总线上。

$t_{DH}$:写信号无效后数据保持时间。

$t_{WR}$:写恢复时间。

在存储控制器中,WE和CS信号是常见的控制信号。

WE代表写使能(Write Enable),用于控制数据的输入。当WE信号为低电平时,数据可以被写入存储器;当WE信号为高电平时,存储器处于读取状态。

CS代表芯片选择(Chip Select),用于选择要操作的存储器芯片。当CS信号为低电平时,与之对应的存储器芯片被选中,并处于可操作状态;当CS信号为高电平时,存储器芯片不可操作。

OE信号是输出使能信号。它用于允许数据在输出引脚上进行传输。当OE信号处于高电平时,输出引脚处于高阻态,数据无法从输出引脚上读取。当OE信号处于低电平时,输出引脚处于正常操作模式,数据可以从输出引脚上读取。

动态随机存取存储器(DRAM)

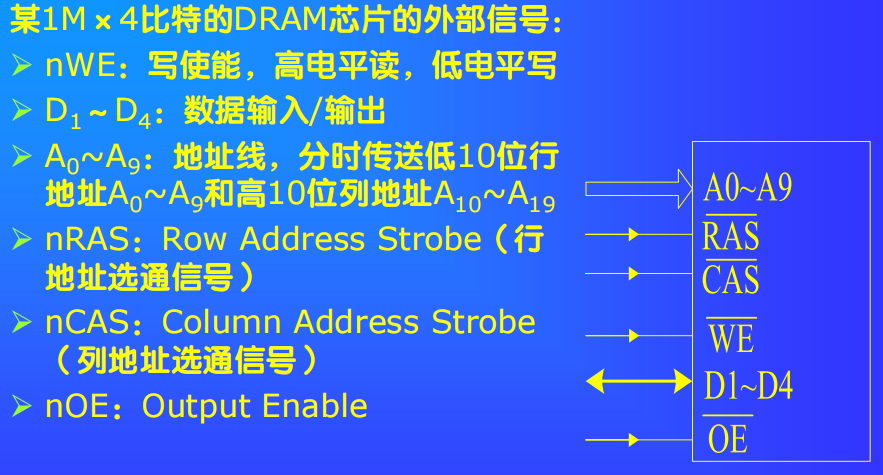

DRAM的管脚信号

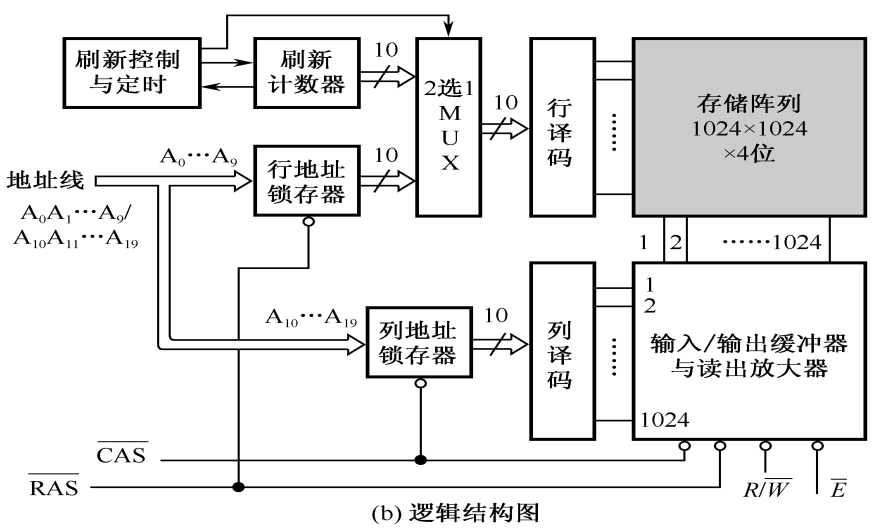

动态存储器框图

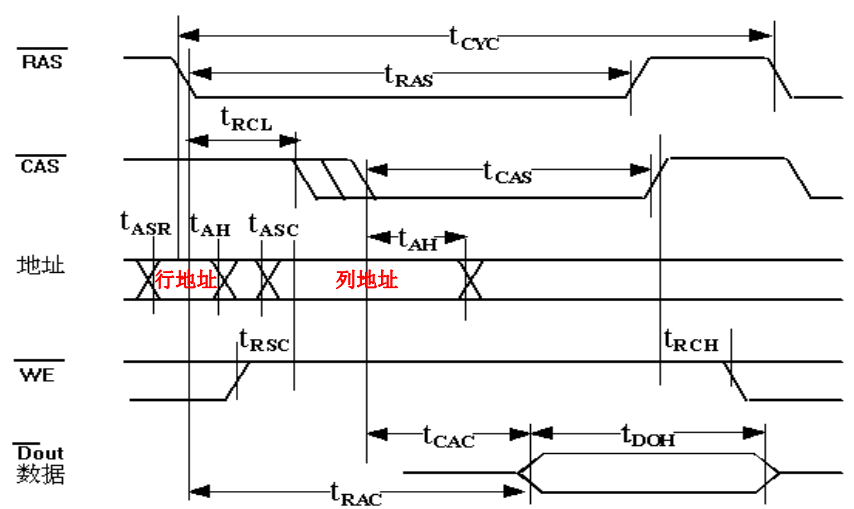

DRAM时序——读周期

行地址有效→行地址选通→列地址有效→列地址选通→数据输出→行选通、列选通及地址撤销

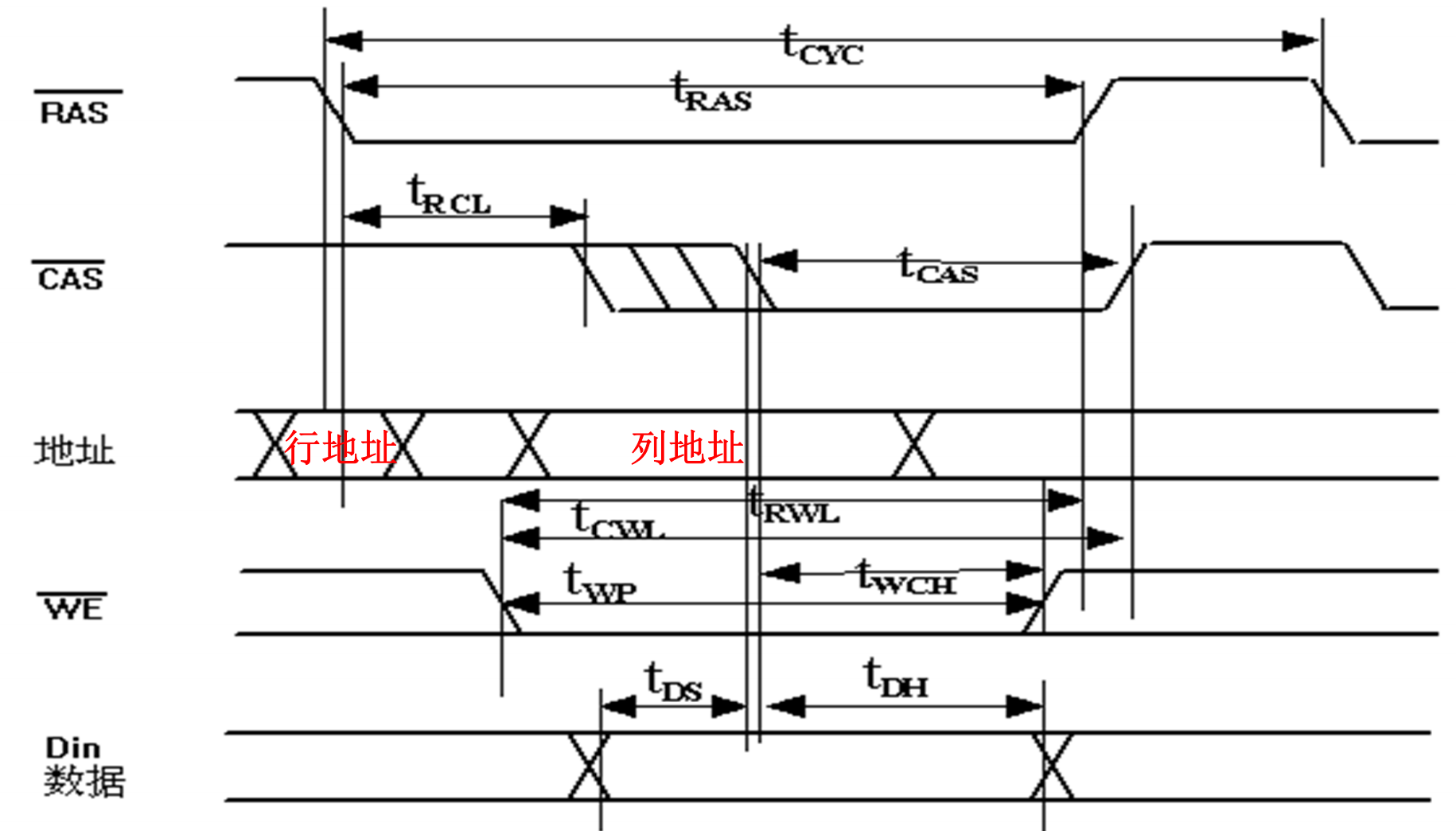

DRAM时序——写周期

行地址有效→行地址选通→列地址、数据有效→列地址选通→数据输入→行选通、列选通及地址撤销

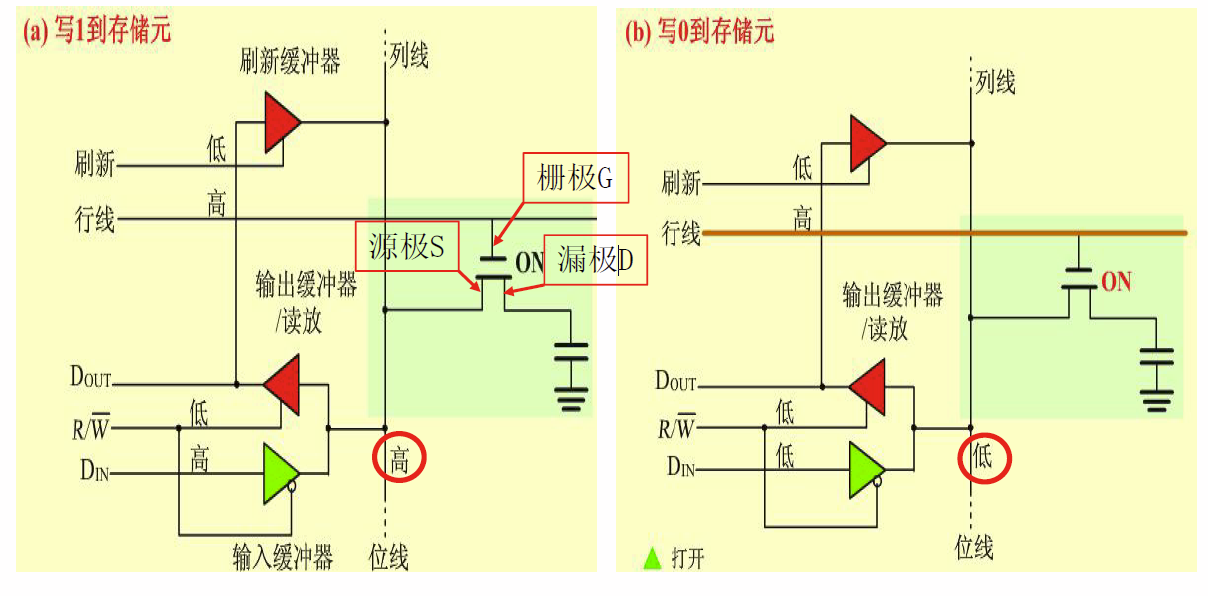

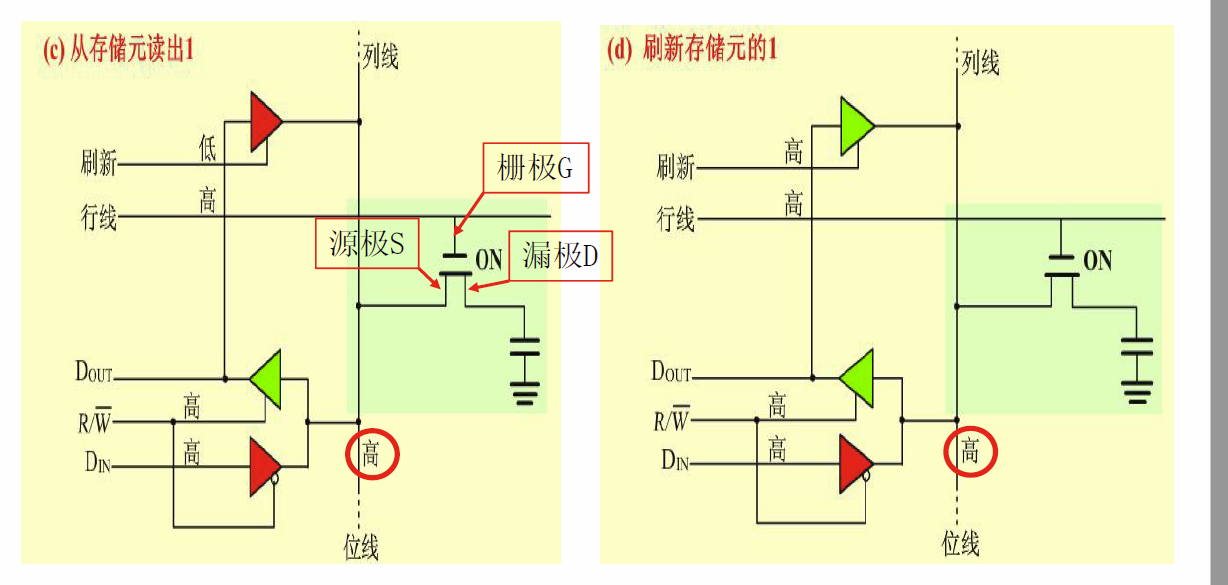

一个DRAM(动态存储器)存储元的写操作过程

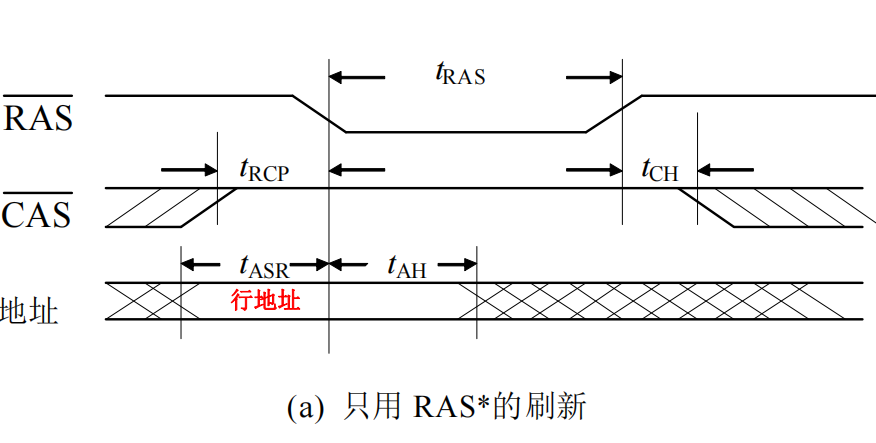

DRAM时序——刷新周期

nRAS only:刷新行地址有效→nRAS有效→刷新行地址和nRAS撤销

读和刷新的过程

DRAM芯片的刷新

DRAM必须进行定期的刷新DRAM芯片内部有刷新电路

一次刷新选中一行中的所有存储位元

刷新操作与读操作类似,只是无须送出数据

刷新方式:

- 集中式

- 分散式

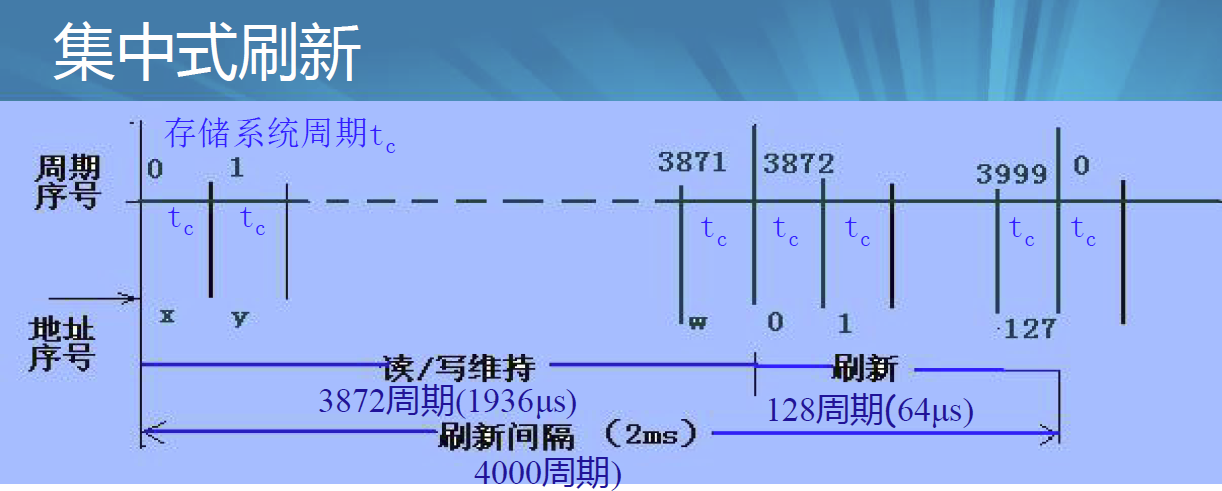

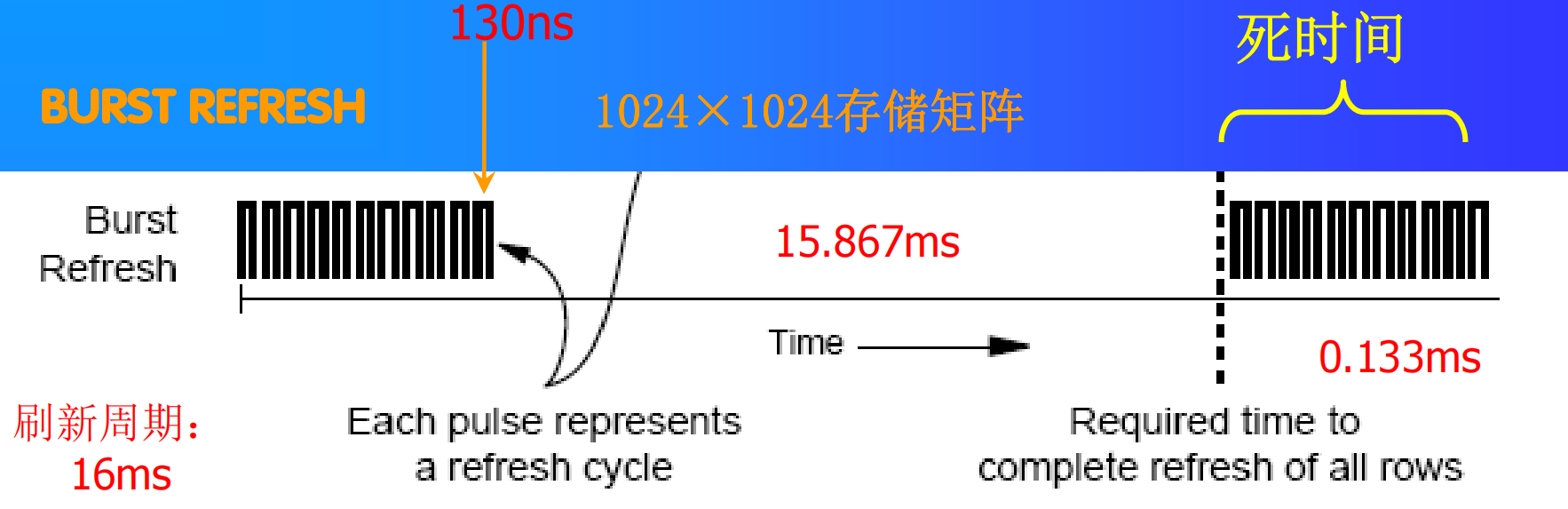

集中式刷新

集中式刷新:在规定的一个刷新周期内,对全部存储单元集中一段时间逐行进行刷新(用专门的时间进行全部刷新)

特点:

(1)对芯片的正常读/写周期不产生影响,存储器系统的平均读写周期接近于存储器件的读写周期

(2)在刷新的过程中不允许读写,会造成芯片“死时间”过长的问题

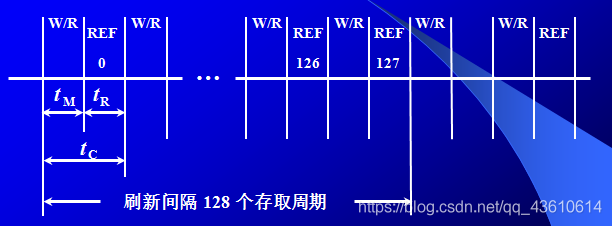

分散式刷新

分散式刷新:对每行存储单元的刷新分散到每个存储周期内完成,将每一行的刷新插入到正常的读/写周期之中(对某一行某芯片进行读写操作后,紧接着刷新,包含在了读写周期内)

优点:无死区

缺陷:

(1)增加了系统周期,进而降低了系统速度

(2)刷新过于频繁

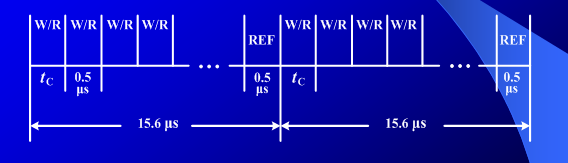

异步式刷新

异步式刷新:前两种方式的结合,缩短了死时间,充分利用了最大刷新间隔为2ms的特点(只要在2ms内对这一行刷新一遍就行)

2000μs÷128≈15.6 μs,即每隔15.6μs刷新一行

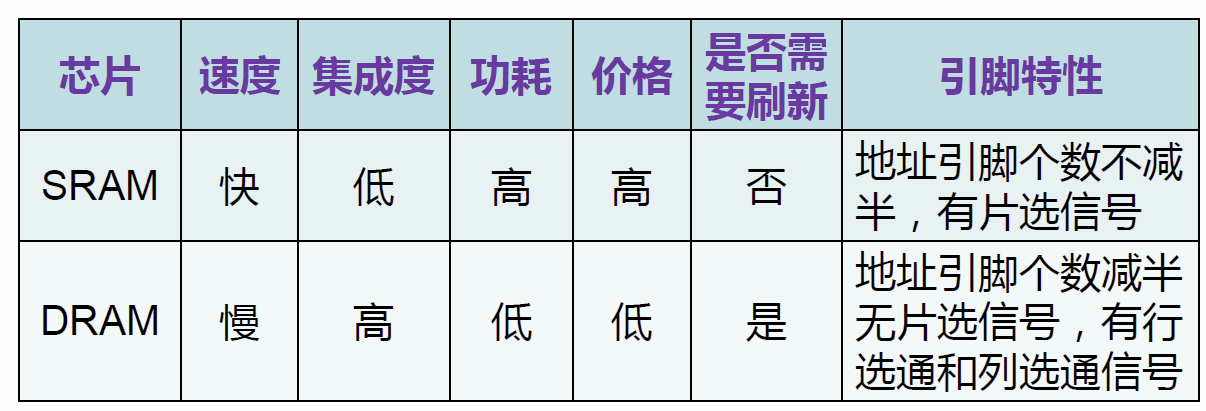

SRAM与DRAM的比较

SRAM:读写速度快,生产成本高,多用于容量较小的高速缓冲存储器。

DRAM:读写速度较慢,集成度高,生产成本低,多用于容量较大的主存储器。

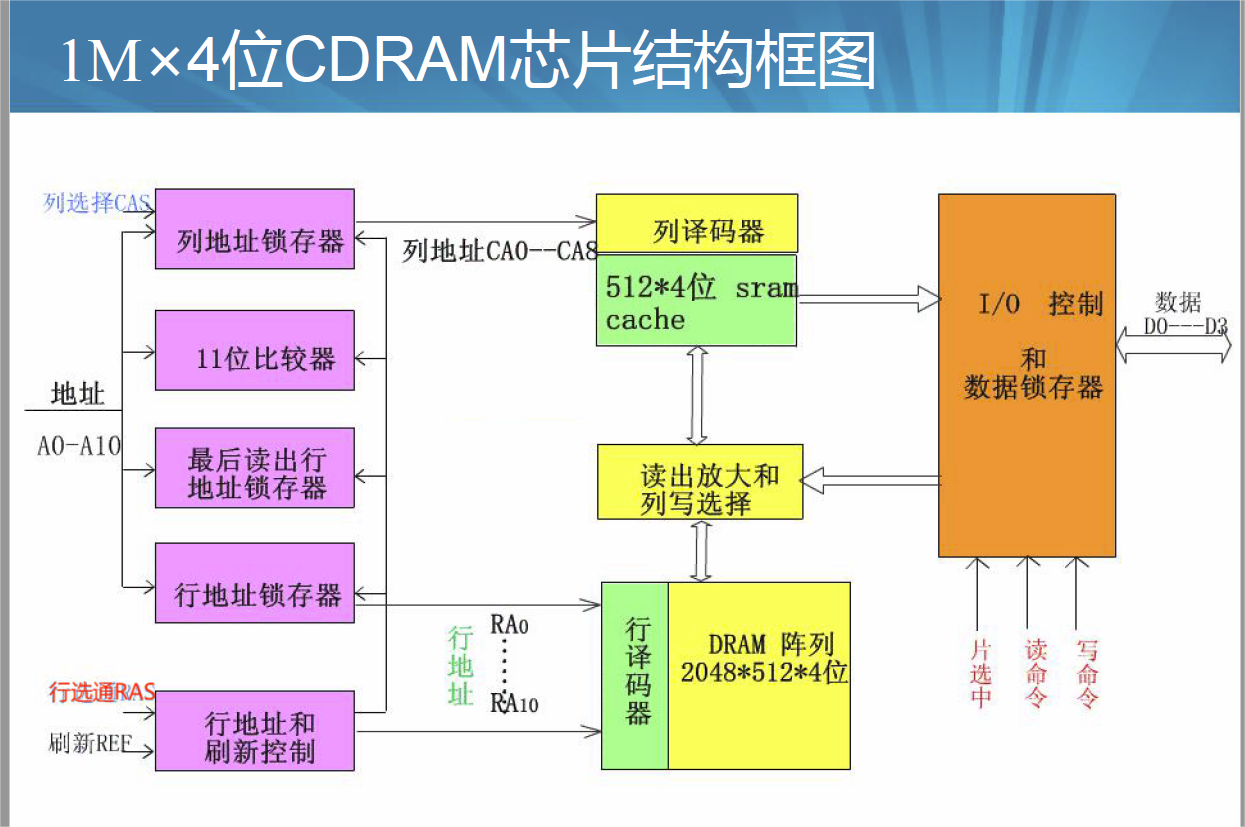

CDRAM 带高速缓冲存储器(cache)的动态存储器

在DRAM主存芯片与CPU交互接口上增加小容量高速缓冲存储器

在DRAM芯片内部增加SRAM构成“Cache”,保存最近访问的一行

增加行地址比较器:如果下次访问的是最近访问过的行,则直接从Cache中读出

CDRAM的优点

- 突发操作速度高

- 在Cache读出期间可同时对DRAM阵列进行刷新

- 芯片内的数据输出路径与输入路径是分开的,读写操作可并行

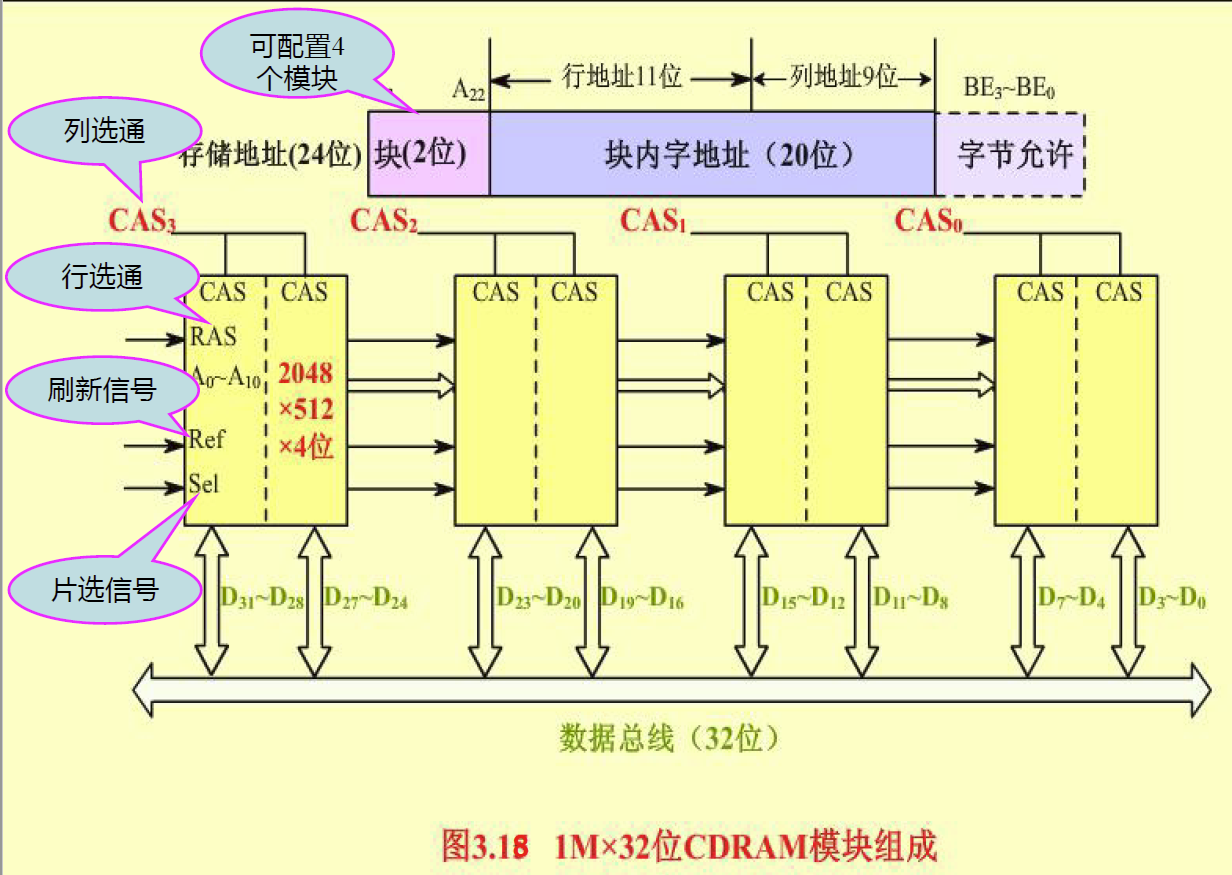

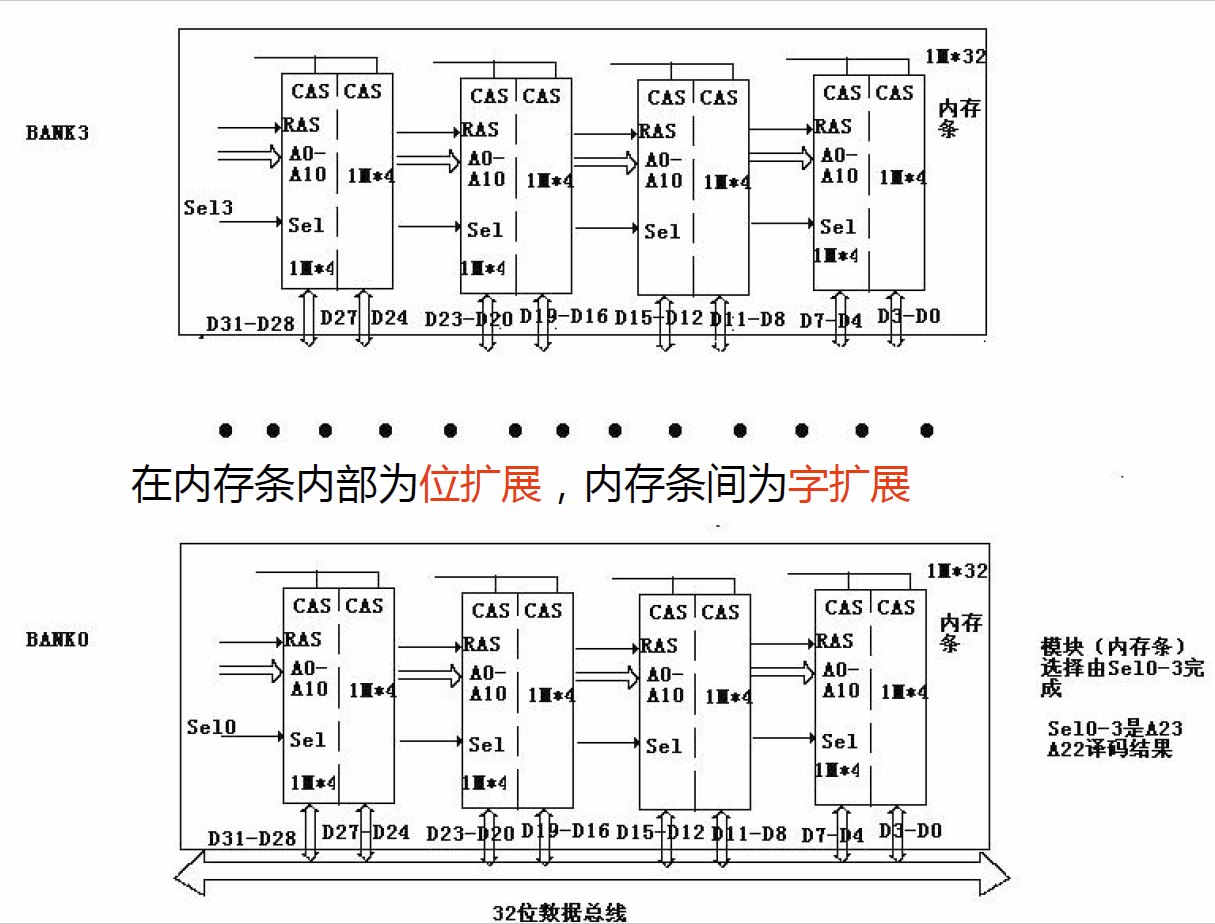

CDRAM存储模块

一片CDRAM的容量为1M×4位,8片这样的芯片可组成1M×32位(4MB)的存储模块

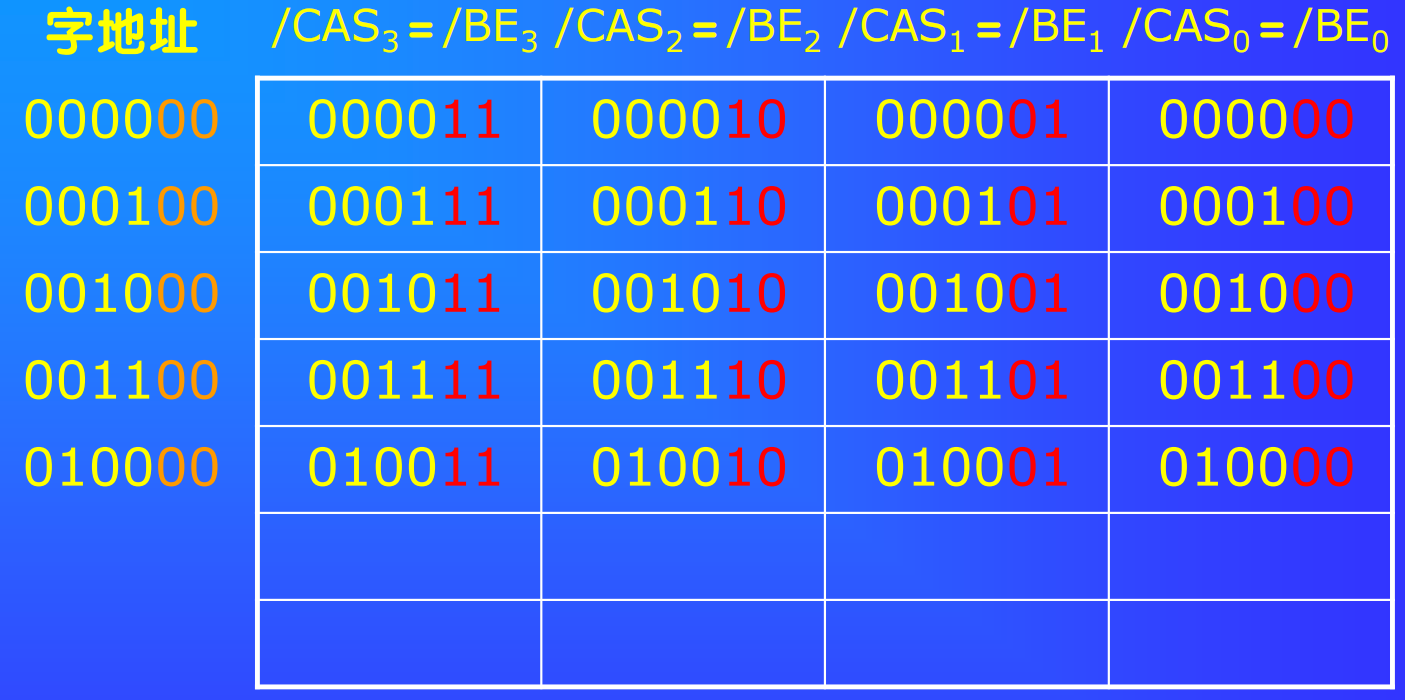

CDRAM内存条地址分配

小端表示,32位总线,按字节编址

闪速(FLASH)存储器

闪速(FLASH)存储器

一种高密度、电擦除、非易失性的只读存储器

既有ROM的优点,又有RAM的优点

FLASH存储器:

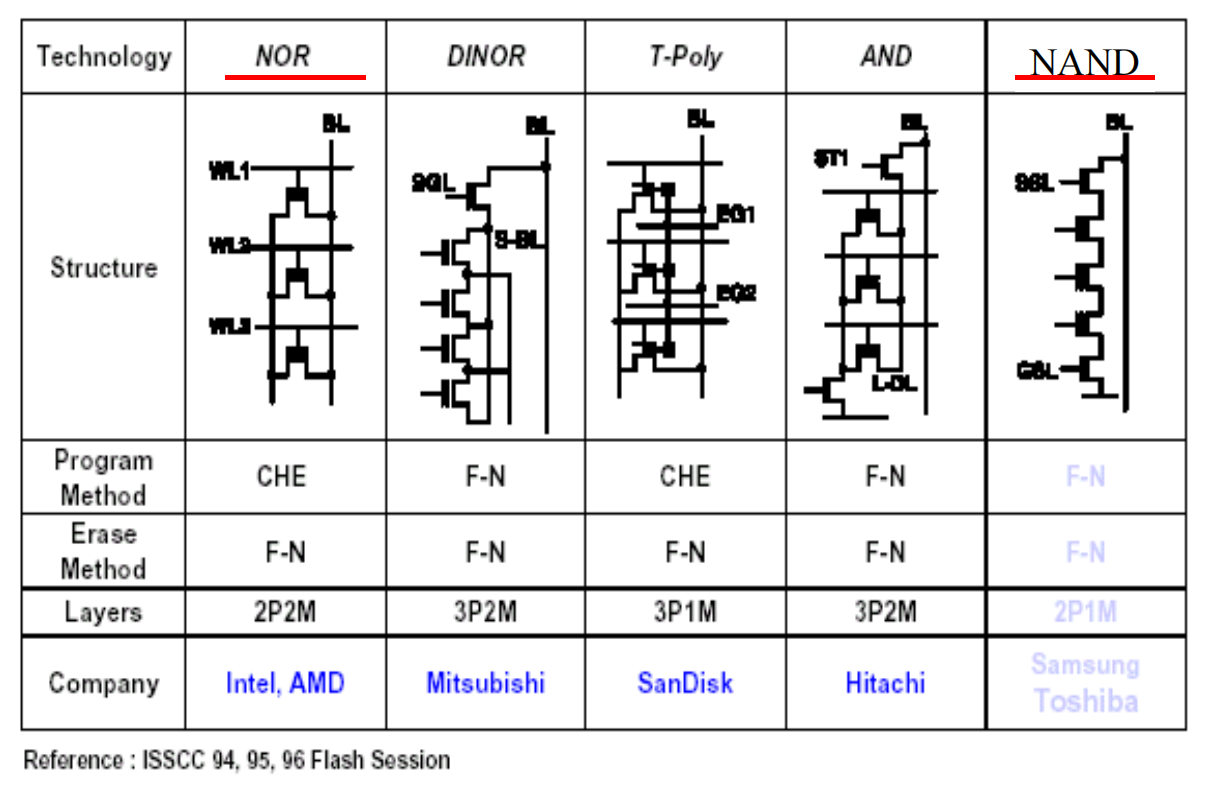

NOR技术

DINOR技术

AND技术

NAND技术

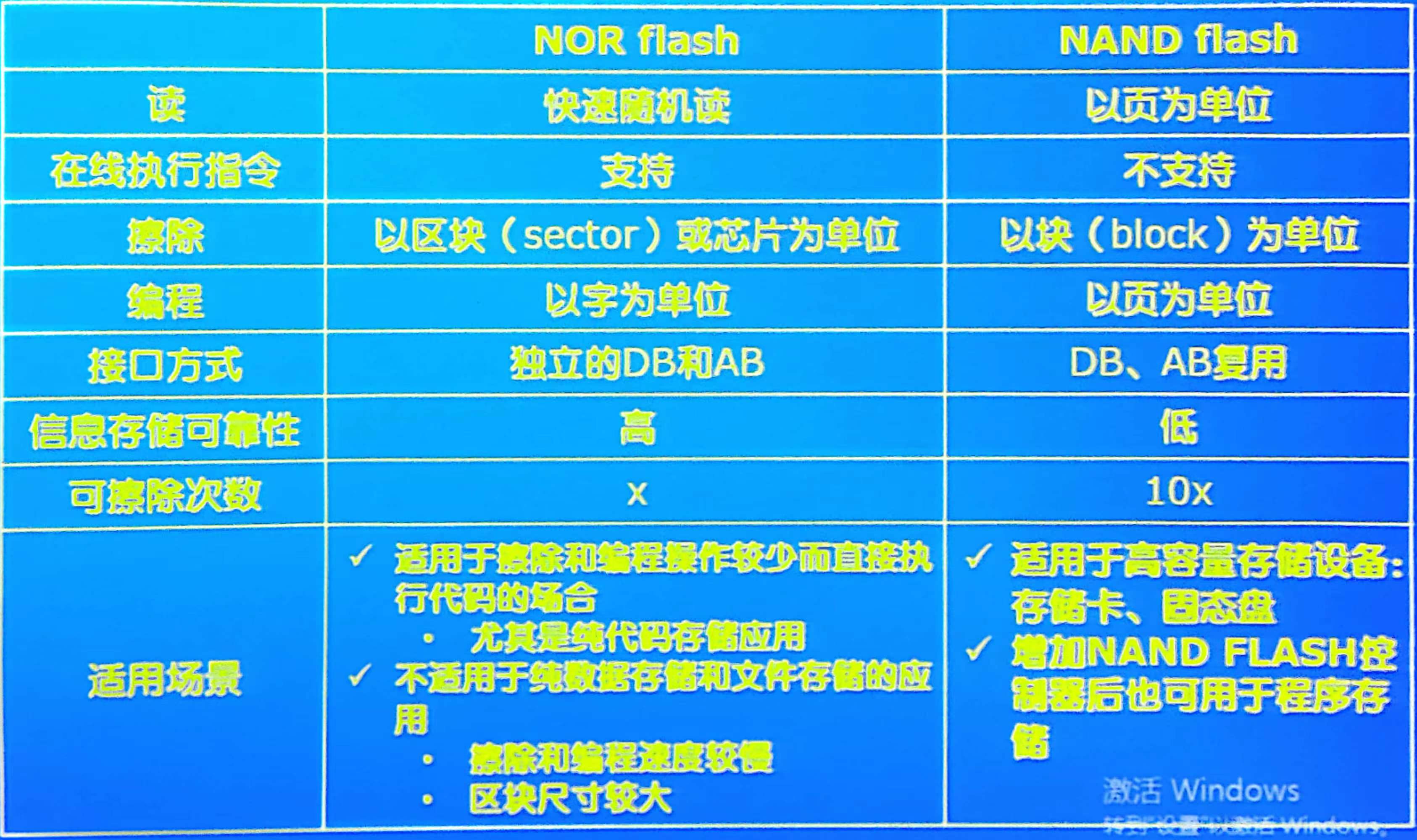

NOR闪存

通常称为线性闪存

- 可以随机读出任意地址的内容,读出速度高

- 存储在其中的指令可直接在线执行

- 可以对单字节或单字进行编程,对单个存储字进行编程,而不影响其他字

- 在对存储器进行重新编程之前,需要对以区块或芯片为单位执行擦除

- 接口与SRAM相似,信息存储的可靠性高,有独立的数据总线和地址总线

- 适用于擦除和编程操作较少而直接执行代码的场合,尤其是纯代码存储应用

- 不适用于纯数据存储和文件存储的应用(擦除和编程速度较慢、区块尺寸较大)

NAND闪存

通常称为非线性闪存

- 非随机访问

- 存储在其中的指令不能够直接在线执行

- 快速编程和快速擦除

- 以页(若干字节)为单位进行读和编程操作

- 以块(几十页)为单位执行擦除操作

- 复用总线,数据、地址采用同一总线,接口与传统ROM不同,可以减少管脚数量降低成本

- 位成本低、位密度高

- 较高的比特错误率,需软件处理坏块(失效块)

- 10倍于NOR flash的擦除次数

- 适用于大容量存储设备:存储卡、固态盘,增加NAND FLASH控制器后也可用于程序存储

并行存储器

CPU和主存储器之间速度上的不匹配限制了计算机系统的工作速度

为了提高CPU和主存之间的数据传输率,采用并行技术的存储器

双端口存储器

多模块交叉存储器

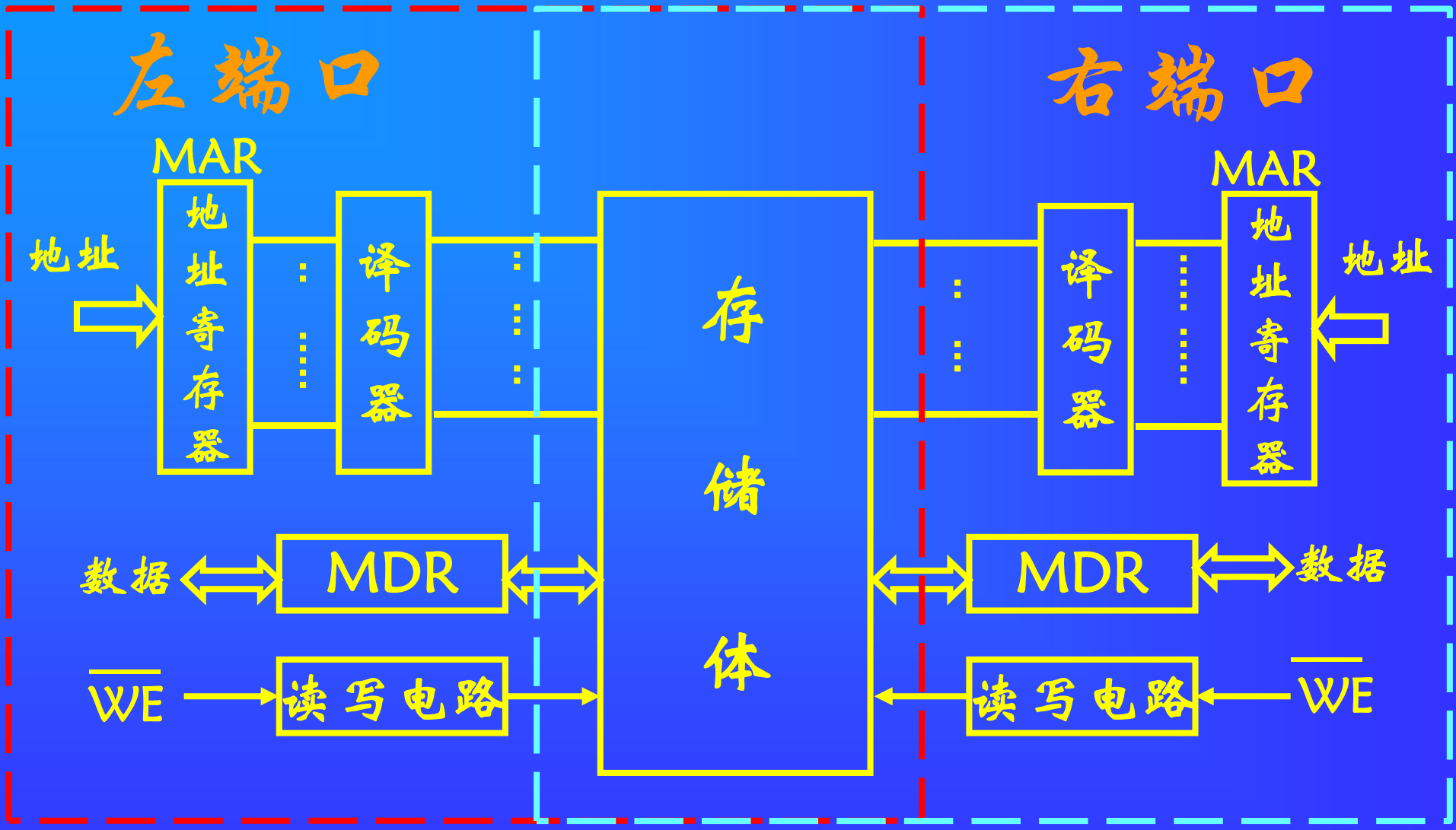

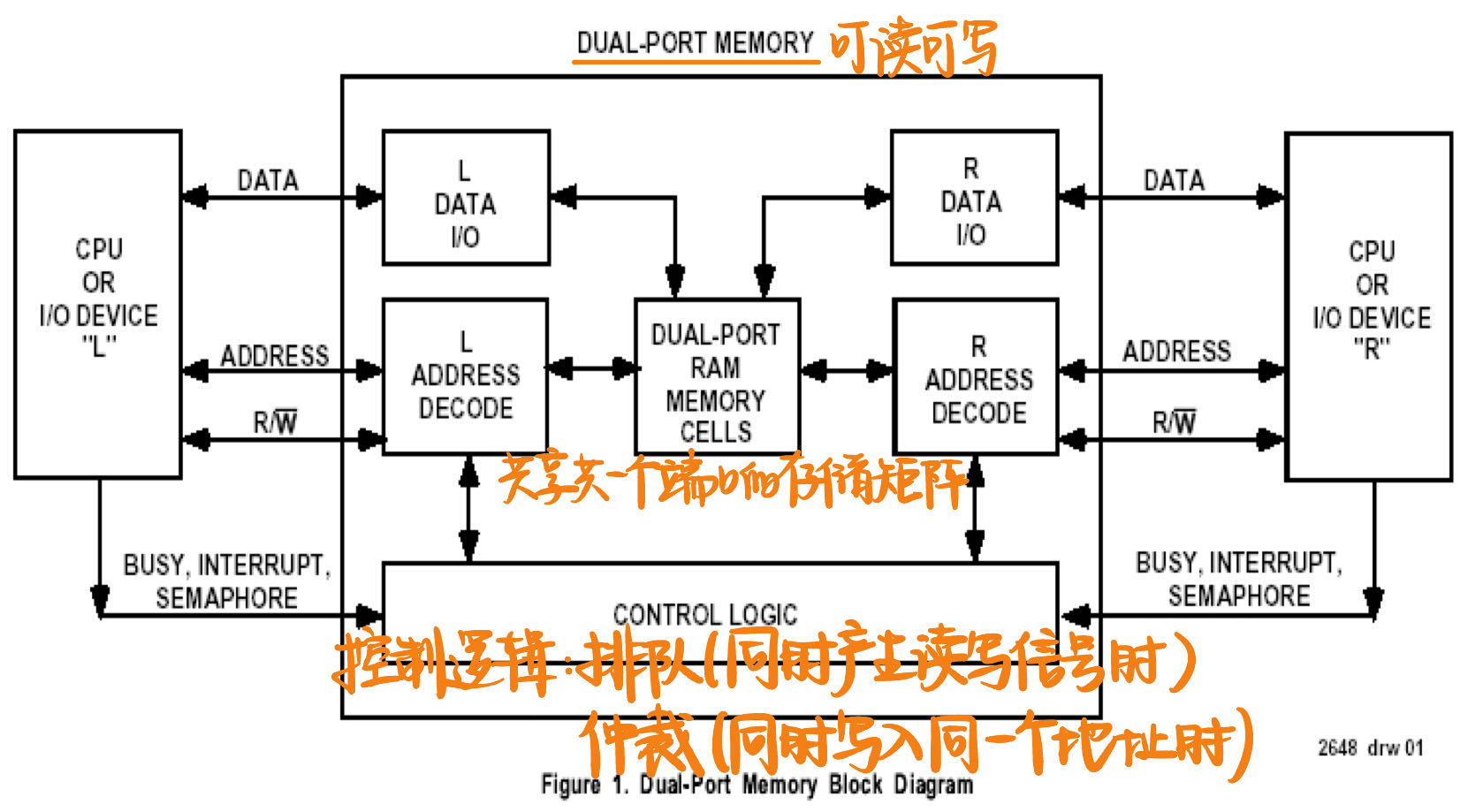

双端口存储器(DPRAM)

双端口存储器:同一个存储器具有两组相互独立的读写控制线路,是一种高速工作的存储器

两个端口分别具有各自的地址线、数据线和控制线

两个端口可对存储器中任何位置上的数据进行独立的存取操作

不仅CPU可以访问主存,其他部件也可不经CPU而直接与主存交换信息

DPRAM的应用方式

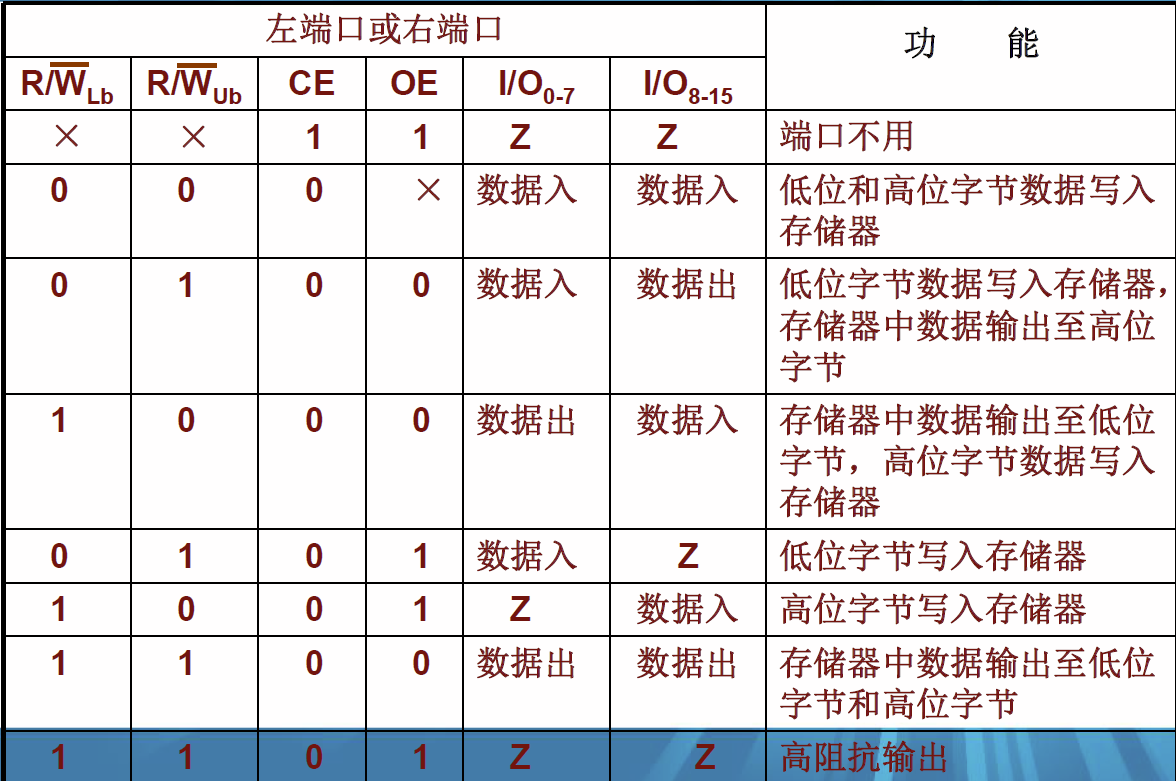

无冲突读写控制

当两个端口的地址不相同时,在两个端口上进行读写操作,一定不会发生冲突。

当任一端口被选中驱动时,就可对整个存储器进行存取,每一个端口都有自己的片选控制(CE)和输出驱动控制(OE)。读操作时,端口的OE(低电平有效)打开输出驱动器,由存储矩阵读出的数据就出现在I/O线上

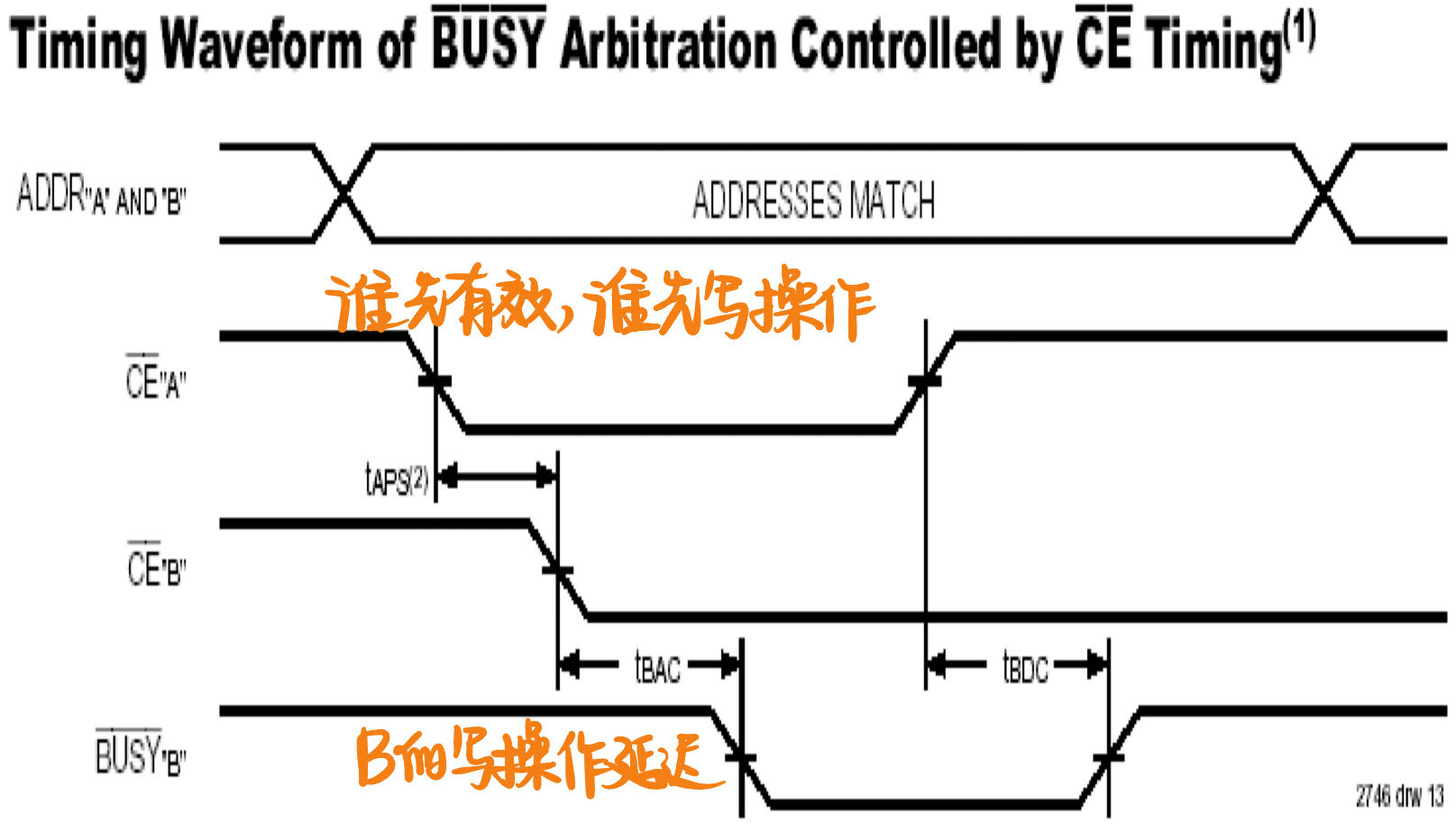

有冲突的读写控制

当两个端口同时存取存储器同一存储单元时,便发生读写冲突。

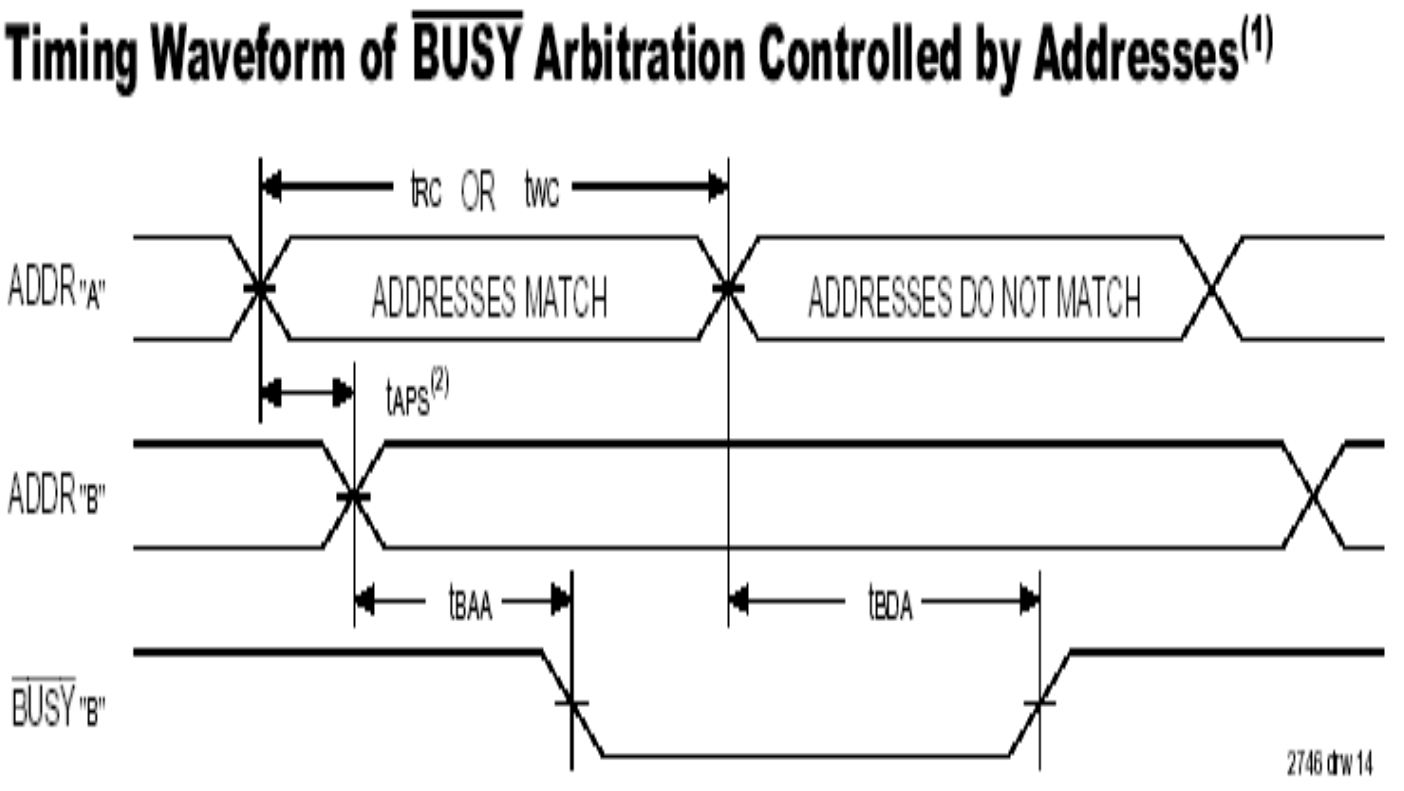

为解决此问题,特设置了BUSY标志。在这种情况下,片上的判断逻辑可以决定对哪个端口优先进行读写操作,而对另一个被延迟的端口置BUSY标志(BUSY变为低电平),即暂时关闭此端口。

设置-BUSY标志,采用仲裁逻辑

仲裁原则:

- CE判断: 如果地址匹配且在CE之前有效,则:片

上的控制逻辑在CEL和CER之间进行判断来选择端口

- 地址有效判断: 如果CE在地址匹配之前先有效,

则:根据预定义的优先级方案选择一个请求进行服务。例如,如果写请求的优先级更高,则编码器将暂停读取操作并执行写入操作。如果两个请求的优先级相同,则编码器可以根据先到先服务(FIFO)的原则来选择一个请求。

左、右端口读写操作的功能判断

……未完待续♬